विषयसूची:

- आपूर्ति

- चरण 1: सीरियल पोर्ट आवश्यकताएँ

- चरण 2: पीआईसी प्रोग्रामिंग आवश्यकताएँ

- चरण 3: जेडीएम विशिष्टता

- चरण 4: सर्किट विवरण

- चरण 5: सिमुलेशन के लिए तैयार करें

- चरण 6: आईसीएसपी के लिए संशोधन

- चरण 7: सिमुलेशन परिणाम

- चरण 8: निष्कर्ष

- चरण 9: और अंत में

वीडियो: जेडीएम प्रोग्रामर समीक्षा: 9 कदम

2024 लेखक: John Day | [email protected]. अंतिम बार संशोधित: 2024-01-30 09:19

जेडीएम एक लोकप्रिय पीआईसी प्रोग्रामर है क्योंकि यह एक सीरियल पोर्ट का उपयोग करता है, कम से कम घटकों का उपयोग करता है और बिजली की आपूर्ति की आवश्यकता नहीं होती है। लेकिन वहाँ भ्रम है, नेट पर कई प्रोग्रामर विविधताओं के साथ, कौन से पीआईसी के साथ काम करते हैं? इस "निर्देश योग्य" में हमने JDM को परीक्षण के लिए रखा और मैं प्रदर्शित करता हूं कि स्पाइस का उपयोग करके सर्किट का अनुकरण कैसे किया जाए जो आपके सभी सवालों का जवाब देगा!

आपूर्ति

एलटीस्पाइस जिसे यहां एनालॉग डिवाइसेज से डाउनलोड किया जा सकता है।

आपको यहां जेडीएम सर्किट फाइलों की भी आवश्यकता है।

चरण 1: सीरियल पोर्ट आवश्यकताएँ

JDM को एक सीरियल पोर्ट मीटिंग EIA232 विनिर्देशन की आवश्यकता होती है, आदर्श रूप से +12/-12 वोल्टेज स्तरों के साथ।

टेक्सास इंस्ट्रूमेंट्स लाइन ड्राइवर MC1488 डेटाशीट के अनुसार (चित्र 3)

आउटपुट प्रतिबाधा = 4V/8mA = 500 ओम।

शॉर्ट सर्किट करंट लिमिट = 12mV, बिना समय सीमा के - चिप को कोई नुकसान नहीं।

लाइन रिसीवर का इनपुट प्रतिबाधा = 3k से 7k ओम अनुशंसित।

पुराने डेस्कटॉप पीसी पर सीरियल पोर्ट इस आवश्यकता को पूरा करने के लिए +12v/-12V का उपयोग करते हैं।

नए लैपटॉप पीसी पर सीरियल पोर्ट कम वोल्टेज का उपयोग करते हैं। जेडीएम काम कर सकता है या नहीं - इसका उत्तर अधिक जटिल है।

चरण 2: पीआईसी प्रोग्रामिंग आवश्यकताएँ

PIC प्रोग्रामिंग आवश्यकताओं से संबंधित जानकारी माइक्रोचिप से प्राप्त की जाती है। उपरोक्त एक विशिष्ट उपकरण के लिए है।

चरण 3: जेडीएम विशिष्टता

क्या मूल जेडीएम वेब साइट समय की धुंध में खो गई है? यह हमें अनुमान लगाता है कि डिजाइनर मूल रूप से विनिर्देश के लिए क्या चाहता था।

- VDD=5V, और अधिकतम IDD=2mA ("सॉकेट में" संस्करण के लिए) प्रदान करें

- VHH=13V, और IHH=0.2mA अधिकतम तक प्रदान करें।

- MCLR वृद्धि समय tVHHR = 1uS अधिकतम।

- ICSP संस्करण लक्ष्य पर 22k पुल-अप के मुकाबले MCLR को कम करने में सक्षम होना चाहिए।

चरण 4: सर्किट विवरण

चित्र JDM1 PICPgm वेब साइट से लिए गए "मानक" JDM सर्किट पर आधारित है। यह "PIC इन सॉकेट" प्रोग्रामर है जहां PIC TX और RTS पिन से पावर लेता है। मूल आरेख को समझना मुश्किल था इसलिए मैंने इसे ऊपर से नीचे तक वर्तमान प्रवाह के सामान्य सम्मेलन का उपयोग करके फिर से तैयार किया है। और मैंने एलईडी संकेतक "रीसेट", "प्रोग" और "आरटीएस" जोड़े हैं जो निर्माण और परीक्षण के दौरान आवश्यक हैं। उम्मीद है कि इनका व्यवहार पर कोई हानिकारक प्रभाव नहीं पड़ेगा।

सर्किट डिजाइन की सामान्य परंपरा सभी आधारों पर समान है, लेकिन जेडीएम की प्रमुख विशेषता यह है कि सीरियल पोर्ट ग्राउंड (जीएनडी) वीडीडी से जुड़ा है। यह भ्रम पैदा करता है क्योंकि सीरियल पोर्ट सिग्नल को GND, PIC सिग्नल को लॉजिक ग्राउंड (VSS) के संबंध में मापा जाता है।

जब TX ऊंचा हो जाता है, तो Q1 दो फॉरवर्ड बायस्ड डायोड के रूप में व्यवहार करता है। (Q1 कलेक्टर सामान्य ट्रांजिस्टर ऑपरेशन की तरह रिवर्स बायस्ड नहीं है)। Q1 कलेक्टर C2 चार्ज करता है, जिसे जेनर (D3) द्वारा VDD+8V पर क्लैंप किया जाता है। Q1 एमिटर प्रोग्राम/वेरीफाई मोड के लिए MCLR को 13V डिलीवर करता है।

जब TX इसे कम करता है, तो कैपेसिटर C3 को D1 के माध्यम से चार्ज किया जाता है और VSS को जेनर (D5) द्वारा VDD-5V पर क्लैंप किया जाता है। साथ ही TX को D1 द्वारा (VSS-0.6) पर क्लैंप किया गया है। Q1 बंद है, C1 अगली प्रोग्रामिंग पल्स के लिए अपना चार्ज रखता है। MCLR 0V पर D2 से जुड़ा हुआ है, इसलिए PIC अब रीसेट हो गया है।

जब आरटीएस अधिक होता है, तो घड़ी पीजीसी को प्रेषित की जाती है। VDD लॉजिक हाई पर D4 क्लैंप PGC। जब आरटीएस कम होता है, तो कैपेसिटर C3 को D6 के माध्यम से चार्ज किया जाता है और VSS को जेनर (D5) द्वारा VDD-5V पर क्लैंप किया जाता है। D6 VSS या लॉजिक 0 पर PGC को क्लैंप करता है।

प्रोग्रामिंग के दौरान, डीटीआर पर भेजे गए डेटा को पीजीडी पर पढ़ा जाता है, जिसे पीआईसी इनपुट के रूप में कॉन्फ़िगर करता है। जब DTR अधिक होता है, Q2 "एमिटर फॉलोअर" के रूप में कार्य करता है और PGD वोल्टेज (VDD-0.6) या तर्क 1 के बारे में होता है। जब DTR कम होता है, तो Q2 एक खराब ट्रांजिस्टर (एमिटर और कलेक्टर पिन उलट) के रूप में कार्य करता है। Q2 PGD को कम खींचता है, जिसे D7 द्वारा VSS या लॉजिक 0 पर क्लैंप किया जाता है।

सत्यापन के दौरान PIC सीरियल पोर्ट पर डेटा भेजने के लिए PGD को आउटपुट के रूप में कॉन्फ़िगर करता है। DTR को उच्च सेट किया जाना चाहिए, और डेटा CTS पर पढ़ा जाता है। जब PGD आउटपुट अधिक होता है, Q2 बंद होता है, CTS = DTR = +12V। जब PGD आउटपुट कम होता है, तो Q2 चालू होता है। Q2 कलेक्टर DTR से करंट (12V+5V)/(1k+1k5)=7mA खींचता है, और CTS को VSS तक कम करता है।

चरण 5: सिमुलेशन के लिए तैयार करें

एलटी स्पाइस डाउनलोड करें, यहां दी गई सर्किट फाइल्स (*.asc) को सेव और ओपन करें। सर्किट को अनुकरण करने के लिए, हमें इसे कुछ इनपुट देना होगा, फिर आउटपुट को "ट्रेस" करना होगा। V1, V2 V3 आउटपुट प्रतिबाधा R11, R12, R13 के साथ 12V सीरियल पोर्ट का अनुकरण करता है।

- V1 TX पर 0.5ms से 4.5ms. तक 2 प्रोग्राम पल्स उत्पन्न करता है

- V2 1.5 से 4.5ms. तक DTR पर डेटा पल्स का बर्स्ट उत्पन्न करता है

- V3 0.5 से 3.5ms. तक RTS पर घड़ी की दालों का फटना उत्पन्न करता है

घटक V4, X1, R15 और R16 सभी सिमुलेशन का हिस्सा हैं।

- V4 डेटा सत्यापित करने के लिए 2.5 से 4.5ms तक 2 दालें उत्पन्न करता है।

- जम्पर X1 PGD पर OUTPUT का अनुकरण करता है।

- R15, R16 VDD और MCLR पर PIC के "लोडिंग" का अनुकरण करते हैं।

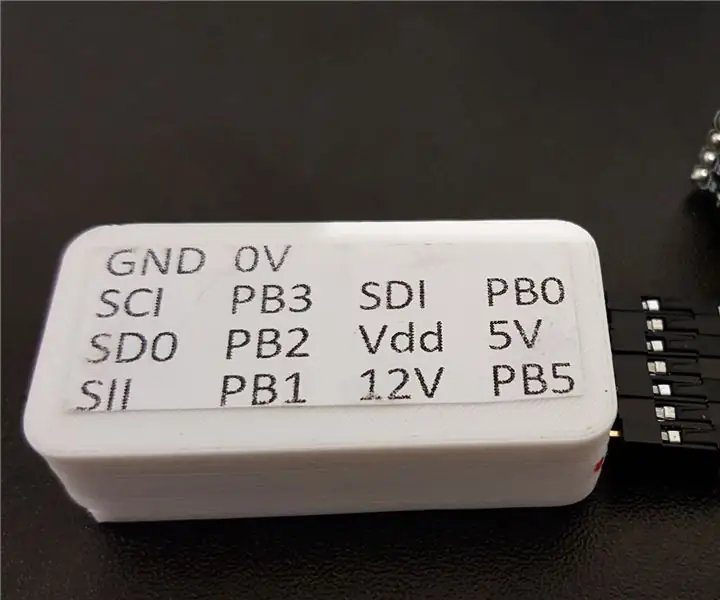

चरण 6: आईसीएसपी के लिए संशोधन

चित्र JDM3 "इन सर्किट" प्रोग्रामिंग के लिए संस्करण दिखाता है। मूल से संशोधन हैं

- ZIF सॉकेट को ICSP कनेक्टर से बदलें।

- PIC अब सप्लाई टू टार्गेट सर्किट (V5) द्वारा संचालित है।

- 5V जेनर (D5) निकालें।

- छोटे 100pF संधारित्र (C4) को लक्ष्य परिपथ पर PIC के बगल में ले जाया जाता है।

- जहां संभव हो एल ई डी सर्किट बोर्ड से बिजली लेते हैं।

- लक्ष्य सर्किट पर MCLR पुल-अप रेसिस्टर (R10) और डायोड (D10) की आवश्यकता होती है।

- चेतावनी। लक्ष्य बोर्ड में "फ्लोटिंग" आपूर्ति होनी चाहिए, आदर्श रूप से एक बैटरी।

- जेडीएम के साथ ही किसी अन्य कंप्यूटर पोर्ट को जोड़कर टार्गेट ग्राउंड (वीएसएस) को कंप्यूटर/पीसी ग्राउंड से न जोड़ें।

JDM1 का अनुकरण करने के बाद, C2 पर लंबे समय तक चार्ज करने की समस्या स्पष्ट हो गई। फिर फ्रूटनबेल को पढ़ने के बाद ऐसा प्रतीत होता है कि C2 और Q1 को मूल में संशोधन के रूप में जोड़ा गया था। मैं नहीं सोच सकता कि C2 और Q1 का उद्देश्य समस्याएँ पैदा करने के अलावा क्या करना है। तो JDM4 के लिए, हम Fruttenboel पर पुराने डिज़ाइन पर वापस लौटते हैं जो समझने में सरल और सीधा है। VSS और VDD+8V के बीच D1 और D3/LED2 क्लैंप MCLR। R1 का मान घटाकर 3k3 कर दिया गया है, जो LED2 को 12V पर रोशन करने के लिए पर्याप्त है।

JDM4 को कमजोर सीरियल पोर्ट के साथ काम करने के लिए भी डिज़ाइन किया गया है। जब TX उच्च (+9V) जाता है, TX वर्तमान स्रोत = (9-8)/(1k +3k3) = 0.2ma, MCLR को उच्च खींचने के लिए पर्याप्त है, हालांकि LED2 को रोशन करने के लिए अपर्याप्त है। जब TX कम हो जाता है (लगभग -7V), TX करंट सिंक = (9-7) / 1k = 2mA। LED1 करंट = (एलईडी के लिए 7-2)/(2k7) = 1.8mA। एमसीएलआर पुल डाउन करंट = 7-5.5/3k3 = 0.5mA।

इस सर्किट का परीक्षण भी किया गया है (जेडीएम 5 सिमुलेशन) यह देखने के लिए कि सीरियल पोर्ट +/- 7 वी न्यूनतम के साथ क्या होता है, जहां वीएचएच = 13 वी को बनाए रखने के लिए अपर्याप्त वोल्टेज है। C1 का उद्देश्य अब स्पष्ट हो गया है, C1 MCLR को एक छोटा + ve बढ़ावा देता है, TX के बढ़ते किनारे पर एक 33us स्पाइक, PIC के प्रोग्रामिंग मोड में प्रवेश करने के लिए पर्याप्त रूप से पर्याप्त है, शायद? लेकिन जम्पर X2 (LED1 को अक्षम करें) को हटा दें क्योंकि MCLR को कम खींचने और LED1 को एक साथ रोशन करने के लिए अपर्याप्त करंट है। जब TX कम हो जाता है, तो TX करंट सिंक = (7V-5.5V)/(1k+3k3) = 0.3mA, पुल-अप R10 के मुकाबले MCLR को कम करने के लिए पर्याप्त है।

चरण 7: सिमुलेशन परिणाम

ग्राफिक फ़ाइलों को देखने के लिए, नीचे दिए गए लिंक पर राइट-क्लिक करना बेहतर है, फिर "नए टैब में लिंक खोलें" चुनें।

सिमुलेशन 1: मूल JDM1 के लिए MCLR, VSS और RTS का पता लगाना। तुरंत अवलोकन 1, 2 और 3 स्पष्ट हैं।

सिमुलेशन 2: एमसीएलआर और वीएसएस का पता लगाना, और संशोधित जेडीएम 2 के लिए आरटीएस, जो पिछली समस्याओं को ठीक करता है।

सिमुलेशन 3: प्रोग्राम मोड में डेटा भेजने वाले JDM2 के लिए PGD, VSS और PGC का ट्रेस। प्रेक्षण 4 3.5mS पर।

सिमुलेशन 4: सत्यापन मोड में JDM2 के लिए PGD, VSS और CTS का ट्रेस (जम्पर X1 डाला गया)। ठीक है

सिमुलेशन 5: JDM3 के लिए MCLR, VSS, PGD और PGC का ट्रेस। सर्किट से बिजली का उपयोग कर आईसीएसपी कई समस्याओं का समाधान करता है।

सिमुलेशन 6: JDM4 के लिए +/- 9V सीरियल पोर्ट के साथ MCLR, VSS, PGD और PGC का ट्रेस। एमसीएलआर तुरंत बढ़ जाता है, पूरी तरह से काम कर रहा है।

सिमुलेशन 7: JDM5 के लिए MCLR, VSS और TX का ट्रेस +/-7V सीरियल पोर्ट और जम्पर X2 के साथ हटा दिया गया। C1 MCLR के बढ़ते किनारे पर एक +ve बूस्ट (स्पाइक) बनाता है, जो MCLR को TX से 13V तक धकेलने के लिए पर्याप्त है।

चरण 8: निष्कर्ष

स्पाइस सर्किट ऑपरेशन के "छिपे हुए रहस्यों" को प्रकट करने में वास्तव में अच्छा है। जाहिर है जेडीएम सर्किट काम करता है और कई पीआईसी चिप्स के साथ संगत है, लेकिन निम्नलिखित अवलोकन संभावित सीमाओं/संगतता मुद्दों/दोषों को प्रकट करते हैं?

- MCLR का लंबा वृद्धि समय जबकि C2 TX की पहली पल्स पर VPP को चार्ज करता है। विनिर्देश विफल रहता है 3.

- सीरियल पोर्ट C2 चार्ज करता है जब TX अधिक हो जाता है और RTS कम हो जाता है। लेकिन RTS में C3 को चार्ज करने का भी काम होता है। जब दोनों एक ही समय में होते हैं तो यह RTS पर अधिक भार पैदा करता है, फलस्वरूप C3 सिमुलेशन पर 2ms पर चार्ज (VSS उगता है) खो देता है। विनिर्देश विफल रहता है 1.

- क्लॉक पल्स 3.5ms पर रुकने के बाद C3 चार्ज खो देता है (VSS बढ़ना शुरू हो जाता है)।

- C2 का उद्देश्य क्या है, इसकी बिल्कुल आवश्यकता है?

समाधान

- संभवतः PICPgm एक सॉफ्टवेयर "वर्क-राउंड" का उपयोग करता है। इसे C2 पर प्रीचार्ज करने के लिए एक लंबी TX पल्स लागू करनी चाहिए, फिर केवल दूसरी TX पल्स के बाद प्रोग्रामिंग मोड में प्रवेश करें? सिमुलेशन के लिए मैंने C2 का मान घटाकर 1uF कर दिया ताकि 1ms का समय बढ़ सके। आदर्श समाधान नहीं है।

- C2 और C3 को विभाजित करें ताकि वे स्वतंत्र रूप से चार्ज हों। JDM2, C2 में एक छोटा संशोधन VSS के बजाय GND को संदर्भित करता है।

- JDM3 द्वारा हल किया गया। ICSP अधिक विश्वसनीय है क्योंकि PIC लक्ष्य सर्किट द्वारा संचालित होता है।

- JDM4 समस्या का समाधान करता है 1. यह C2 को पूरी तरह से समाप्त करने वाला एक सीधा डिजाइन है।

चरण 9: और अंत में

हलवा का सबूत खाने में है। यह जेडीएम काम करता है इसलिए इसका इस्तेमाल करते रहें।

और मेरी सिफारिशें हैं:

- सॉकेट प्रोग्रामिंग और 12V सीरियल पोर्ट के लिए JDM2 का उपयोग करें,

- ICSP प्रोग्रामर के लिए JDM4 का उपयोग करें और +/- 9V से ऊपर के सीरियल पोर्ट,

- +/- 7V से ऊपर के सीरियल पोर्ट के लिए हटाए गए जम्पर X2 के साथ JDM4 का उपयोग करें।

सन्दर्भ:

एनालॉग डिवाइसेस एलटी स्पाइस

पिकपजीएम

फ्रूटनबेल

चालाकी से और अधिक पीआईसी परियोजनाओं का पालन करें

सिफारिश की:

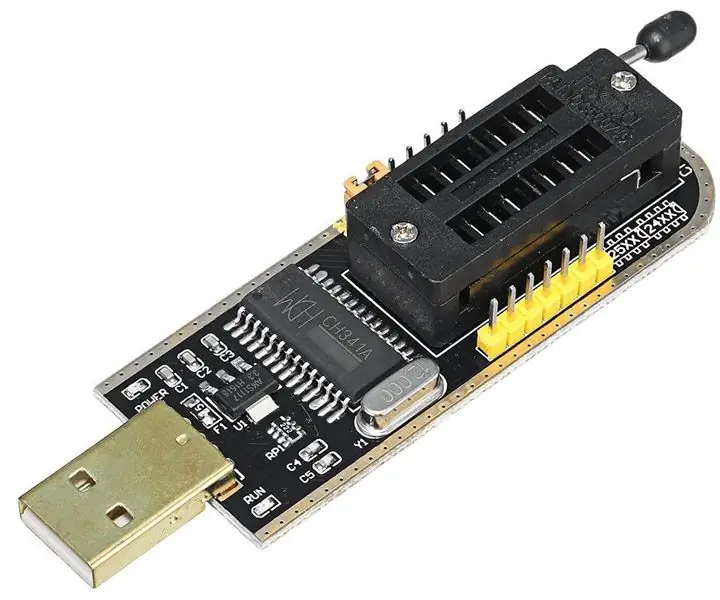

CH341A प्रोग्रामर: 8 कदम

CH341A प्रोग्रामर: मैंने हाल ही में एक CH341A मिनी प्रोग्रामर खरीदा है। मिनी प्रोग्रामर ठीक है और 24 और 24 श्रृंखला चिप्स को प्रोग्राम करने के लिए उपयोग किया जा सकता है। यह बहुत कम लागत वाला है लेकिन काफी उपयोगी है क्योंकि मैं इसका उपयोग अपने कंप्यूटर BIOS और राउटर फर्मवेयर को फ्लैश करने के लिए कर सकता हूं। WCH ने कृपया जारी किया है

Arduino ISP के रूप में -- AVR में बर्न हेक्स फ़ाइल -- एवीआर में फ्यूज -- प्रोग्रामर के रूप में Arduino: 10 कदम

Arduino ISP के रूप में || AVR में बर्न हेक्स फ़ाइल || एवीआर में फ्यूज || अरुडिनो प्रोग्रामर के रूप में:………………अधिक वीडियो के लिए कृपया मेरे YouTube चैनल को सब्सक्राइब करें……यह लेख आईएसपी के रूप में आर्डिनो के बारे में सब कुछ है। यदि आप हेक्स फ़ाइल अपलोड करना चाहते हैं या यदि आप एवीआर में अपना फ्यूज सेट करना चाहते हैं तो आपको प्रोग्रामर खरीदने की आवश्यकता नहीं है, आप कर सकते हैं

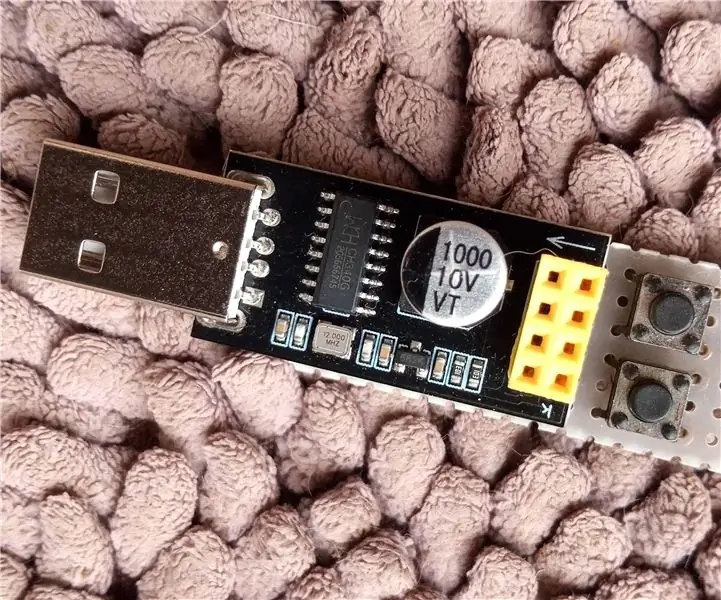

ESP-01 प्रोग्रामर हैक - आसान एक ::: 6 कदम

ESP-01 प्रोग्रामर हैक - द इज़ी वन :: हाय ESPers, इस निर्देश में मैं आपको ESP-01 / ESP8266-01 / ES-01 मॉड्यूल के लिए प्रोग्रामर बनाने के लिए एक सरल हैक दिखा रहा हूँ। हम में से अधिकांश ने इस मॉड्यूल के लिए प्रोग्रामर के रूप में एक Arduino बोर्ड या FTDI USB-TTL उपकरणों का उपयोग किया है। दोनों विधि ठीक काम करती है। लेकिन टी

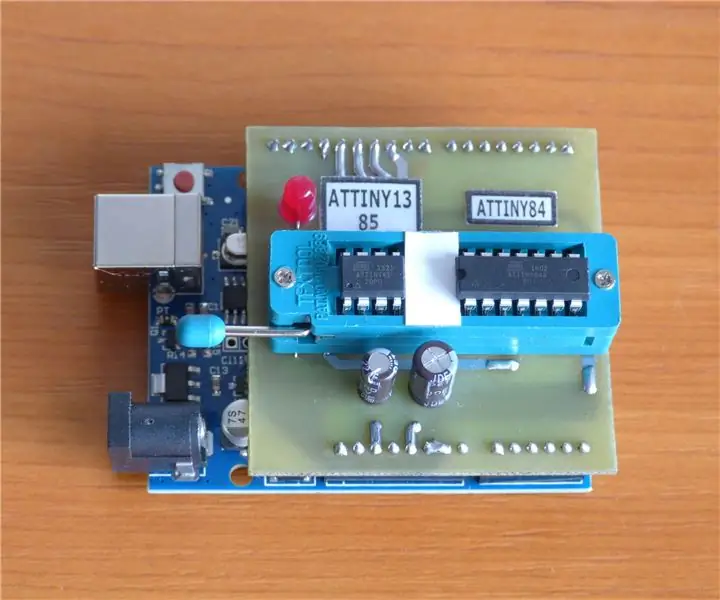

Arduino UNO के साथ ATTINY माइक्रोकंट्रोलर्स के लिए एक छोटा प्रोग्रामर: 7 कदम

Arduino UNO के साथ ATTINY माइक्रोकंट्रोलर्स के लिए एक छोटा प्रोग्रामर: वर्तमान में उनकी बहुमुखी प्रतिभा, कम कीमत के कारण ATTINY श्रृंखला माइक्रोकंट्रोलर का उपयोग करना दिलचस्प है, लेकिन यह भी तथ्य है कि उन्हें Arduino IDE जैसे वातावरण में आसानी से प्रोग्राम किया जा सकता है। Arduino मॉड्यूल के लिए डिज़ाइन किए गए प्रोग्राम हो सकते हैं आसानी से ट्रांसफर

एटीटीनी एचवी प्रोग्रामर: 4 कदम

ATTiny HV प्रोग्रामर: यह निर्देश एक ESP8266 और एक ब्राउज़र आधारित यूजर इंटरफेस का उपयोग करते हुए ATTiny प्रोग्रामिंग उपयोगिता के लिए है।