विषयसूची:

- चरण 1: एडीसी वास्तुकला

- चरण 2: आंतरिक सर्किट

- चरण 3: बाहरी सर्किट

- चरण 4: I2C निर्देश पढ़ें

- चरण 5: परिणाम

वीडियो: एडीसी करंट सेंस कैसे बनाएं: 5 कदम

2024 लेखक: John Day | [email protected]. अंतिम बार संशोधित: 2024-01-30 09:20

इस निर्देशयोग्य में हम वर्णन करेंगे कि SLG46855V में 8-बिट एनालॉग-टू-डिजिटल कनवर्टर (ADC) को कैसे लागू किया जाए जो I2C के माध्यम से MCU के साथ लोड करंट और इंटरफ़ेस को समझ सके। इस डिज़ाइन का उपयोग विभिन्न करंट सेंसिंग अनुप्रयोगों जैसे कि एमीटर, फॉल्ट डिटेक्शन सिस्टम और फ्यूल गेज के लिए किया जा सकता है।

नीचे हमने आवश्यक चरणों का वर्णन किया है कि एडीसी करंट सेंस बनाने के लिए समाधान को कैसे प्रोग्राम किया गया है। हालाँकि, यदि आप केवल प्रोग्रामिंग का परिणाम प्राप्त करना चाहते हैं, तो पहले से पूर्ण की गई ग्रीनपैक डिज़ाइन फ़ाइल को देखने के लिए ग्रीनपैक सॉफ़्टवेयर डाउनलोड करें। ग्रीनपैक डेवलपमेंट किट को अपने कंप्यूटर में प्लग करें और एडीसी करंट सेंस बनाने के लिए प्रोग्राम को हिट करें।

चरण 1: एडीसी वास्तुकला

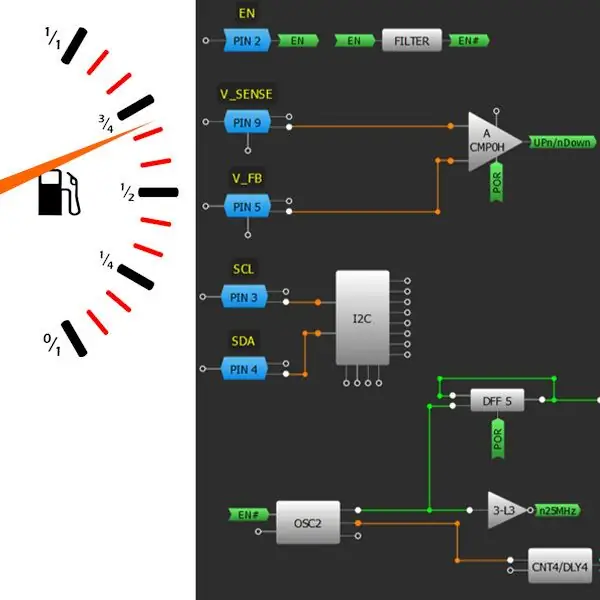

एडीसी में अनिवार्य रूप से एक एनालॉग तुलनित्र और एक डिजिटल-से-एनालॉग कनवर्टर (डीएसी) शामिल है। तुलनित्र इनपुट वोल्टेज बनाम डीएसी आउटपुट वोल्टेज को महसूस करता है, और बाद में नियंत्रित करता है कि डीएसी इनपुट कोड को बढ़ाना या घटाना है, जैसे कि डीएसी आउटपुट इनपुट वोल्टेज में परिवर्तित हो जाता है। परिणामी DAC इनपुट कोड ADC डिजिटल आउटपुट कोड बन जाता है।

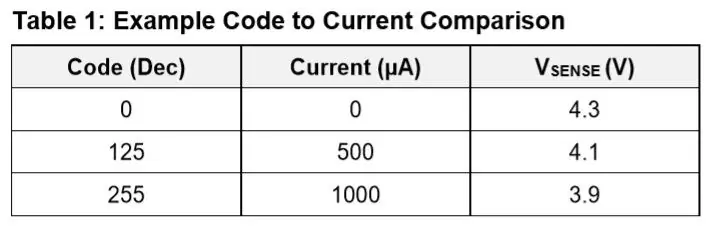

हमारे कार्यान्वयन में, हम एक पल्स-चौड़ाई मॉडुलन (पीडब्लूएम) नियंत्रित प्रतिरोधी नेटवर्क का उपयोग करके एक डीएसी बनाते हैं। हम ग्रीनपैक का उपयोग करके आसानी से एक सटीक डिजिटल नियंत्रित पीडब्लूएम आउटपुट बना सकते हैं। फ़िल्टर किए जाने पर PWM हमारा एनालॉग वोल्टेज बन जाता है और इस प्रकार एक प्रभावी DAC के रूप में कार्य करता है। इस दृष्टिकोण का एक विशिष्ट लाभ यह है कि केवल प्रतिरोधक मानों को समायोजित करके शून्य कोड और पूर्ण पैमाने (समान रूप से ऑफसेट और लाभ) के अनुरूप वोल्टेज सेट करना आसान है। उदाहरण के लिए, एक उपयोगकर्ता आदर्श रूप से तापमान सेंसर से शून्य कोड पढ़ना चाहता है जिसमें 4.3 V के अनुरूप कोई करंट (0 μA) नहीं होता है, और 3.9 V (तालिका 1) के अनुरूप 1000 μA पर पूर्ण पैमाने पर कोड होता है। इसे केवल कुछ प्रतिरोधक मान सेट करके आसानी से कार्यान्वित किया जाता है। एडीसी रेंज को ब्याज की सेंसर रेंज से मेल खाने से, हम एडीसी रिज़ॉल्यूशन का सबसे बड़ा उपयोग करते हैं।

इस आर्किटेक्चर के लिए एक डिजाइन विचार यह है कि आंतरिक पीडब्लूएम आवृत्ति को एडीसी अद्यतन दर से बहुत तेज होना चाहिए ताकि इसके नियंत्रण लूप के कमजोर व्यवहार को रोका जा सके। कम से कम यह 256 से विभाजित एडीसी डेटा काउंटर घड़ी से अधिक लंबा होना चाहिए। इस डिज़ाइन में, एडीसी अद्यतन अवधि 1.3312 एमएस पर सेट है।

चरण 2: आंतरिक सर्किट

लचीला एडीसी डायलॉग सेमीकंडक्टर एएन-1177 में प्रस्तुत डिजाइन पर आधारित है। एडीसी काउंटर को देखने के लिए घड़ी की गति 1 मेगाहर्ट्ज से बढ़ाकर 12.5 मेगाहर्ट्ज कर दी गई है क्योंकि एसएलजी 46855 में 25 मेगाहर्ट्ज की घड़ी उपलब्ध है। यह बेहतर नमूना रिज़ॉल्यूशन के लिए बहुत तेज़ अद्यतन दर की अनुमति देता है। ADC डेटा क्लॉक को देखने वाली LUT बदल जाती है इसलिए PWM DFF कम होने पर यह 12.5 मेगाहर्ट्ज सिग्नल से गुजरेगी।

चरण 3: बाहरी सर्किट

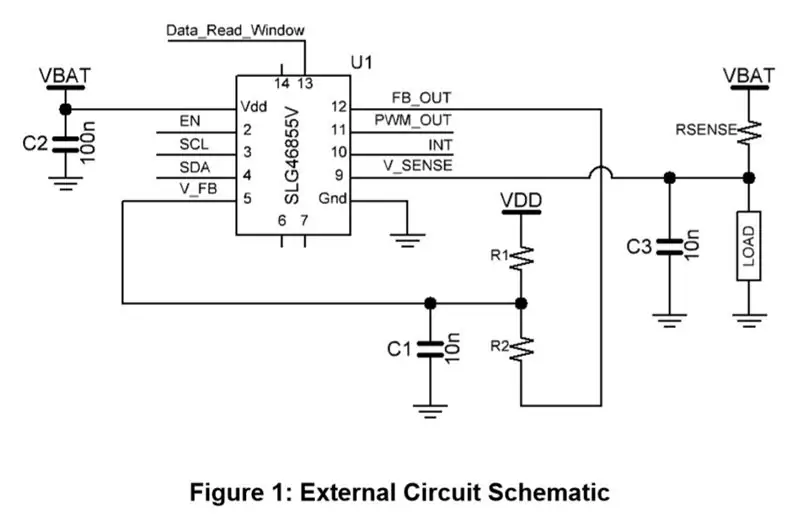

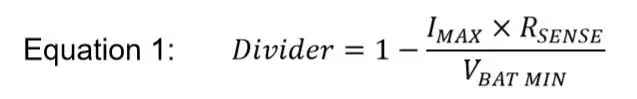

एक बाहरी रोकनेवाला और संधारित्र नेटवर्क का उपयोग पीडब्लूएम को एक एनालॉग वोल्टेज में बदलने के लिए किया जाता है जैसा कि चित्र 1 में सर्किट योजनाबद्ध में दिखाया गया है। मानों की गणना अधिकतम वर्तमान के लिए अधिकतम रिज़ॉल्यूशन के लिए की जाती है जो डिवाइस को समझ में आएगा। इस लचीलेपन को प्राप्त करने के लिए, हम प्रतिरोधों R1 और R2 को VDD और ग्राउंड के समानांतर जोड़ते हैं। एक रेसिस्टर डिवाइडर VBAT को वोल्टेज रेंज के निचले हिस्से में विभाजित करता है। अपेक्षित न्यूनतम VBAT के लिए विभक्त अनुपात को समीकरण 1 का उपयोग करके हल किया जा सकता है।

चरण 4: I2C निर्देश पढ़ें

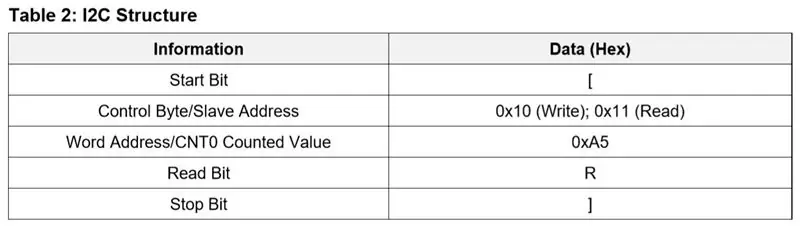

तालिका 1 CNT0 में संग्रहीत डेटा को वापस पढ़ने के लिए I2C कमांड संरचना का वर्णन करती है। I2C कमांड के लिए स्टार्ट बिट, कंट्रोल बाइट, वर्ड एड्रेस, रीड बिट और स्टॉप बिट की आवश्यकता होती है।

CNT0 काउंटेड वैल्यू को वापस पढ़ने के लिए I2C कमांड का एक उदाहरण नीचे लिखा गया है:

[0x10 0xA5] [0x11 आर]

गिना गया मान जो वापस पढ़ा जाता है, वह ADC कोड मान होगा। उदाहरण के तौर पर, डायलॉग की वेबसाइट पर इस एप्लिकेशन नोट की ज़िप फ़ाइल में एक Arduino कोड शामिल है।

चरण 5: परिणाम

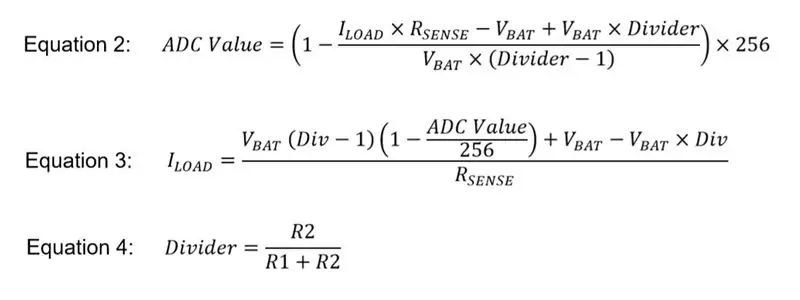

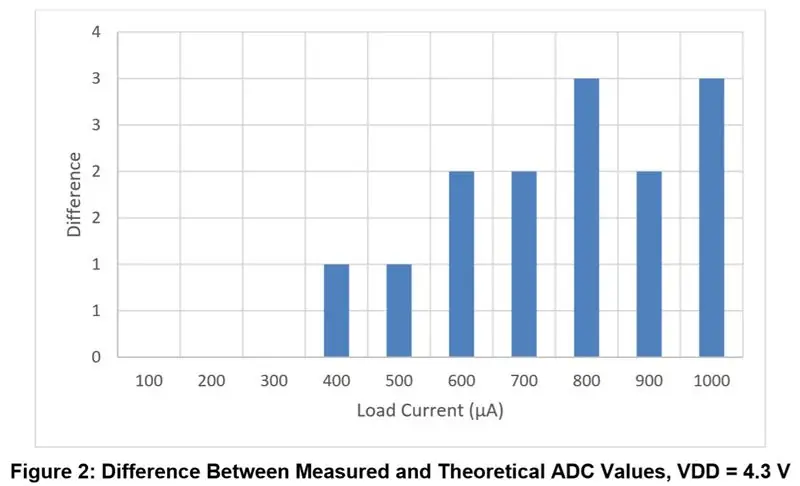

ADC करंट सेंस डिज़ाइन की सटीकता का परीक्षण करने के लिए, किसी दिए गए लोड करंट और VDD स्तर पर मापे गए मानों की तुलना एक सैद्धांतिक मूल्य से की गई। सैद्धांतिक एडीसी मूल्यों की गणना समीकरण 2 के साथ की गई थी।

ILOAD जो ADC मान से संबंधित है, समीकरण 3 के साथ पाया जाता है।

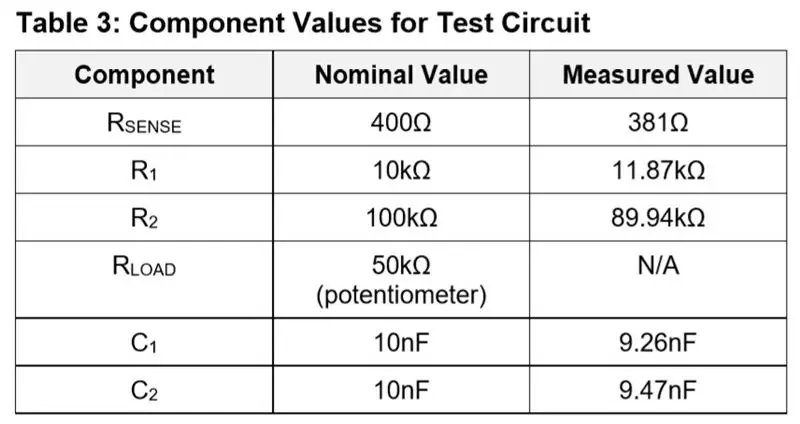

निम्नलिखित परिणामों के लिए मैंने तालिका 3 में दिखाए गए इन घटक मानों का उपयोग किया।

ILOAD रूपांतरण के लिए ADC मान के रिज़ॉल्यूशन की गणना तालिका 2 में मापे गए मानों के साथ समीकरण 3 का उपयोग करके की जा सकती है और ADC मान 1 पर सेट किया गया है। 3.9 V के VBAT के साथ रिज़ॉल्यूशन 4.96 µA/div है।

एडीसी करंट सेंस सर्किट को 3.6 वी के न्यूनतम वीडीडी स्तर पर अधिकतम 1100 μA और 381 सेंस रेसिस्टर के साथ अनुकूलित करने के लिए, आदर्श विभक्त गुणांक 0.884 होगा, जो समीकरण 1 पर आधारित होगा। तालिका में दिए गए मानों के साथ 2, वास्तविक विभक्त का विभक्त गुणांक 0.876 है। चूंकि यह थोड़ा कम है, यह थोड़ी बड़ी लोड करंट रेंज की अनुमति देगा, इसलिए ADC मान पूरी रेंज के करीब हैं, लेकिन ओवरफ्लो नहीं होंगे। वास्तविक विभक्त मान की गणना समीकरण 4 से की जाती है।

ऊपर (आंकड़े 2-6, टेबल 4-6) तीन वोल्टेज स्तरों पर सर्किट के माप हैं: 4.3 वी, 3.9 वी, और 3.6 वी। प्रत्येक स्तर मापा और सैद्धांतिक एडीसी मूल्यों के बीच अंतर प्रदर्शित करने वाला ग्राफ प्रदर्शित करता है। सैद्धांतिक मानों को निकटतम पूर्ण पूर्णांक तक पूर्णांकित किया जाता है। तीन वोल्टेज स्तरों पर अंतर की तुलना करने के लिए एक सारांश ग्राफ है। बाद में सैद्धांतिक एडीसी मूल्यों और विभिन्न वोल्टेज स्तरों पर लोड करंट के बीच सहसंबंध को प्रदर्शित करने वाला एक ग्राफ है।

निष्कर्ष

डिवाइस को तीन वोल्टेज स्तरों पर परीक्षण किया गया था: 3.6 वी, 3.9 वी, और 4.3 वी। इन वोल्टेज की श्रेणी में एक पूर्ण लिथियम आयन बैटरी होती है जो अपने नाममात्र स्तर तक निर्वहन करती है। तीन वोल्टेज स्तरों में से, यह देखा गया है कि चुने हुए बाहरी सर्किट के लिए डिवाइस आमतौर पर 3.9 V पर अधिक सटीक था। मापा और सैद्धांतिक एडीसी मूल्यों के बीच का अंतर ७००-१००० µ ए के लोड धाराओं पर केवल १ दशमलव मान बंद था। दी गई वोल्टेज रेंज पर, मापा गया एडीसी मान सबसे खराब स्थिति में नाममात्र स्थितियों से 3 दशमलव अंक ऊपर था। विभिन्न वीडीडी वोल्टेज स्तरों को अनुकूलित करने के लिए प्रतिरोधी विभक्त में और समायोजन किए जा सकते हैं।

सिफारिश की:

स्टेपर मोटर के लिए हाई करंट ड्राइवर कैसे बनाएं: 5 कदम

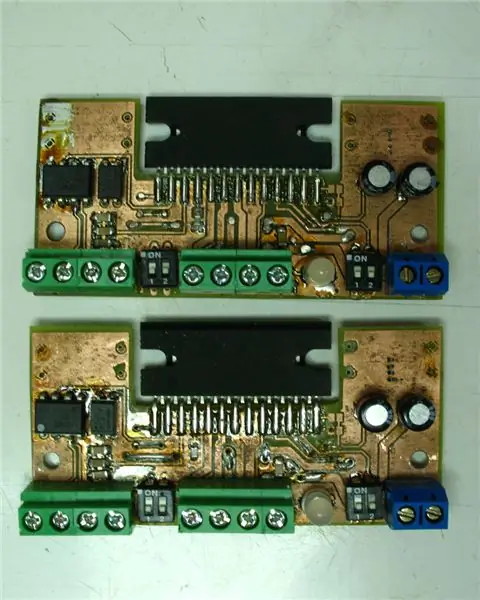

स्टेपर मोटर के लिए हाई करंट ड्राइवर कैसे बनाएं: यहां हम देखेंगे कि तोशिबा के TB6560AHQ कंट्रोलर का उपयोग करके स्टेपर मोटर ड्राइवर कैसे बनाया जाता है। यह एक पूर्ण विशेषताओं वाला नियंत्रक है जिसे इनपुट के रूप में केवल 2 चर की आवश्यकता होती है और यह सभी कार्य करता है। चूँकि मुझे इनमें से दो की आवश्यकता थी, इसलिए मैंने इन दोनों का उपयोग करके बनाया है

शेली सेंस - वायरलेस पावर्ड (डब्ल्यूपीसी क्यूई स्टैंडर्ड): 5 कदम (चित्रों के साथ)

शेली सेंस - वायरलेस पावर्ड (डब्ल्यूपीसी क्यूई स्टैंडर्ड): कृपया ध्यान दें: इस ट्यूटोरियल के बाद आप अपनी वारंटी खो देंगे और आप अपने शेली सेंस को तोड़ने का जोखिम भी उठाएंगे। इसे तभी करें जब आप जानते हैं कि आप क्या कर रहे हैं और यदि आप जोखिमों से अवगत हैं। शेली सेंस सभी को समझने के लिए एक अद्भुत उत्पाद है

फ्लाईबैक ट्रांसफॉर्मर या स्पीकर पर एडीसी से पीडब्लूएम का उपयोग करके Arduino के साथ गाने चलाएं: 4 कदम

फ्लाईबैक ट्रांसफॉर्मर या स्पीकर पर ADC से PWM का उपयोग करके Arduino के साथ गाने चलाएं: हैलो दोस्तों, यह मेरे एक और निर्देश का दूसरा भाग है (जो बहुत मुश्किल था), मूल रूप से, इस परियोजना में, मैंने अपने Arduino पर ADC और TIMERS का उपयोग किया है। ऑडियो सिग्नल को PWM सिग्नल में बदलें। यह मेरे पिछले निर्देश की तुलना में बहुत आसान है

ऑटो लाइट सेंस के साथ ग्लास मार्टिनी नाइट लाइट: 3 कदम

ग्लास मार्टिनी नाइट लाइट ऑटो लाइट सेंस के साथ: एक लाइट सेंसिंग एलईडी नाइट लाइट का एक सरल हैक एक सौम्य रात की रोशनी बनाने के लिए )3-6 एल ई डी (यदि आप चाहते हैं

गिटार स्पीकर बॉक्स कैसे बनाएं या अपने स्टीरियो के लिए दो कैसे बनाएं: 17 कदम (चित्रों के साथ)

अपने स्टीरियो के लिए गिटार स्पीकर बॉक्स या बिल्ड टू कैसे बनाएं: मैं चाहता था कि मेरे द्वारा बनाए जा रहे ट्यूब amp के साथ एक नया गिटार स्पीकर जाए। स्पीकर मेरी दुकान में बाहर रहेगा इसलिए इसे कुछ खास होने की जरूरत नहीं है। Tolex कवरिंग बहुत आसानी से क्षतिग्रस्त हो सकती है इसलिए मैंने हल्की रेत के बाद बाहरी काले रंग का छिड़काव किया