विषयसूची:

- चरण 1: पुन: पूर्वाग्रह चरण

- चरण 2: करंट सेंसिंग रेसिस्टर

- चरण 3: ट्रांस-चालन एम्पलीफायर

- चरण 4: इंस्ट्रुमेंटेशन एम्पलीफायर

- चरण 5: इनपुट चरण और अंशांकन

- चरण 6: उन्नत सामग्री: वर्णक्रमीय रिसाव (डीसी)

- चरण 7: उन्नत सामग्री: वर्णक्रमीय रिसाव (एसी)

- चरण 8: उन्नत सामग्री: सैद्धांतिक लाभ-कारक

- चरण 9: उन्नत सामग्री: पीए शिफ्ट

वीडियो: AD5933 के साथ जैव प्रतिबाधा विश्लेषण (BIA): 9 चरण

2024 लेखक: John Day | [email protected]. अंतिम बार संशोधित: 2024-01-30 09:21

मुझे शरीर संरचना माप के लिए जैव प्रतिबाधा विश्लेषक बनाने में दिलचस्पी है और मेरी यादृच्छिक खोजों ने वेंडरबिल्ट विश्वविद्यालय में 2015 बायोमेडिकल इंस्ट्रुमेंटेशन क्लास से एक डिज़ाइन ढूंढा। मैंने डिजाइन के माध्यम से काम किया है और इसमें थोड़ा सुधार किया है। मैं अपने निष्कर्ष आपके साथ साझा करना चाहता हूं। इस "वॉक-थ्रू" से आप जो उपयोग कर सकते हैं उसे लें यदि कुछ स्पष्ट नहीं है तो कृपया सुधार का सुझाव दें। हो सकता है कि किसी दिन मैं अपने विचार को अधिक समेकित रूप में लिखूं, लेकिन अभी के लिए मुझे आशा है कि आप यहां जो कुछ भी देखते हैं उसका उपयोग कर सकते हैं। (यदि आपको लगता है कि आप इसे लिख सकते हैं और सुधार कर सकते हैं, तो आपका स्वागत है)

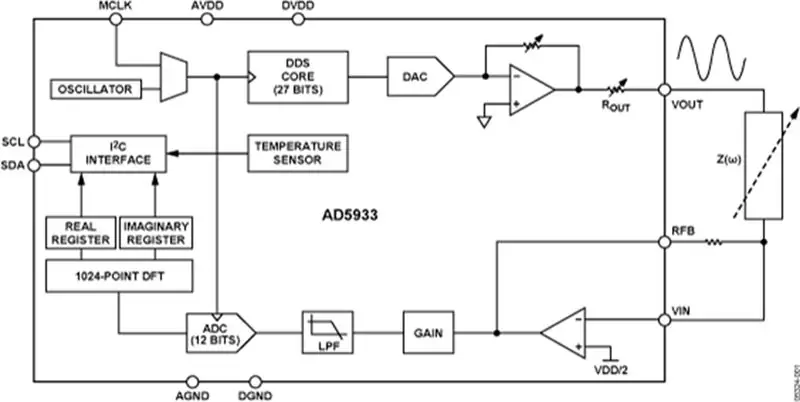

टेडी

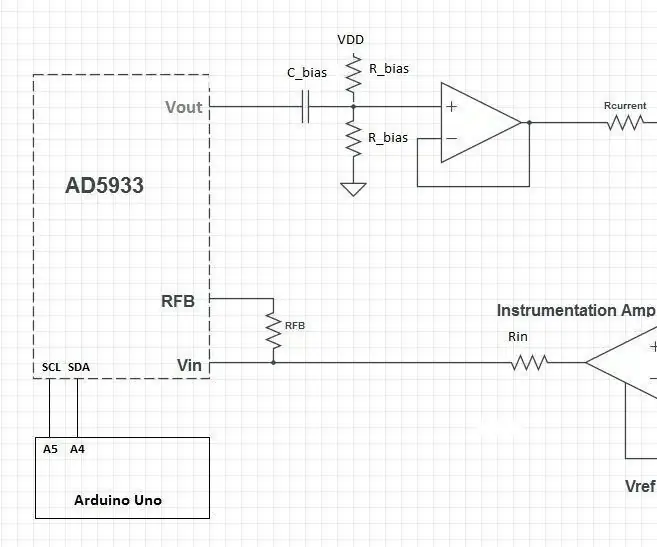

इस डिज़ाइन में AD5933 चिप और शरीर के साथ AD5933 को इंटरफ़ेस करने के लिए एक कस्टम एनालॉग फ्रंट-एंड (AFE) शामिल है। AD5933 तब माप करता है और परिणाम तब एक माइक्रोकंट्रोलर (जैसे एक Arduino) द्वारा संसाधित किए जा सकते हैं।

यदि आप बिजली की आपूर्ति के रूप में Arduino का उपयोग करने की योजना बना रहे हैं, तो सुनिश्चित करें कि परिचालन और उपकरण एम्पलीफायर (op-amps और in-amps) तथाकथित "एकल आपूर्ति" वोल्टेज का समर्थन करते हैं और रेल-टू-रेल चश्मा हैं।

(निम्नलिखित में मैं 5V की बिजली आपूर्ति (एक Arduino से) और AD5933 पर रेंज 1 सेटिंग का उपयोग करूंगा।)

चरण 1: पुन: पूर्वाग्रह चरण

एएफई का पहला भाग एक पुन: पूर्वाग्रह चरण है। आउटपुट वोल्टेज सिग्नल सप्लाई वोल्टेज रेंज (VDD/2) के बीच में केंद्रित नहीं होता है। सिग्नल के डीसी हिस्से को ब्लॉक करने के लिए कैपेसिटर का उपयोग करके और इसे वोल्टेज स्प्लिटर के माध्यम से भेजकर डीसी ऑफ़सेट को सिग्नल में वापस जोड़ने के लिए इसे ठीक किया जाता है।

दो पुन: पूर्वाग्रह प्रतिरोधक तब तक किसी भी मूल्य के हो सकते हैं जब तक वे समान हों। टोपी का विशिष्ट मूल्य भी महत्वपूर्ण नहीं है।

पुन: पूर्वाग्रह चरण एक उच्च पास फिल्टर की तरह काम करता है और इसलिए इसकी कटऑफ आवृत्ति होती है:

f_c = 1 / (2*pi * (0.5*R) * C)

सुनिश्चित करें कि कटऑफ आवृत्ति आपके द्वारा उपयोग की जाने वाली न्यूनतम आवृत्ति से कुछ दशक कम है। यदि आप अपने आवेदन में 1kHz का उपयोग करने की योजना बना रहे हैं, तो आपको कैप्स और प्रतिरोधक मानों के लिए जाना चाहिए जो आपको 1-10 हर्ट्ज के क्रम पर कटऑफ आवृत्ति प्रदान करेंगे।

इस चरण का अंतिम भाग एक वोल्टेज अनुयायी होने के लिए स्थापित एक सेशन-amp है। यह सुनिश्चित करने के लिए है कि रोकनेवाला मान अगले चरण में हस्तक्षेप न करें

चरण 2: करंट सेंसिंग रेसिस्टर

अगले चरण का पहला भाग करंट सेंसिंग रेसिस्टर है। इस रोकनेवाला के माध्यम से वर्तमान वही होगा जो एम्पलीफायर शरीर के माध्यम से बनाए रखने की कोशिश करेगा। सुनिश्चित करें कि करंट IEC6060-1 सुरक्षा मानकों का अनुपालन करता है*:

1 किलोहर्ट्ज़ की आवृत्तियों से नीचे शरीर के माध्यम से अधिकतम 10 माइक्रोएम्प्स (आरएमएस) की अनुमति है। 1kHz से ऊपर की आवृत्तियों पर निम्नलिखित समीकरण अधिकतम अनुमत धारा देता है:

अधिकतम एसी वर्तमान <(kHz में न्यूनतम आवृत्ति) * 10 माइक्रोएम्प्स (आरएमएस)

एक एसी सिग्नल के शिखर आयाम और उसके आरएमएस मान के बीच संबंध है: पीक = sqrt(2) * RMS। (१० माइक्रोएम्प्स आरएमएस १४ माइक्रोएम्प्स शिखर आयाम के अनुरूप हैं)

रोकनेवाला पर ओम नियम का उपयोग करके हम उस प्रतिरोधक मान की गणना कर सकते हैं जो सुरक्षा मानक का अनुपालन करेगा। हम AD5933 से उत्तेजना वोल्टेज और अधिकतम वर्तमान मूल्य का उपयोग करते हैं:

यू = आर * आई => आर = यू / आई

उदा. रेंज 1 सेटिंग Upeak = 3V / 2 = 1.5V (या 1V @3.3V) का उपयोग करके

ऊपर से 14 माइक्रोएम्प पीक वैल्यू का उपयोग करके मुझे कम से कम 107kOhms. का रेसिस्टर वैल्यू मिलता है

सन्दर्भ:

* एनालॉग डिवाइस: "बॉडी वॉर्न सिस्टम के लिए बायो-इम्पेडेंस सर्किट डिजाइन"

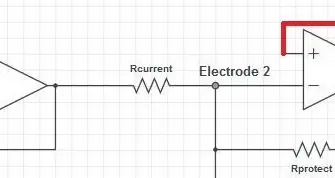

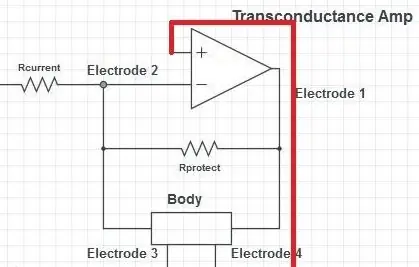

चरण 3: ट्रांस-चालन एम्पलीफायर

वर्तमान संवेदन रोकनेवाला के बाद एक नकारात्मक प्रतिक्रिया विन्यास में एक op-amp है। यह एक तथाकथित लोड-इन-द-लूप सेटअप है। op-amp का धनात्मक इनपुट टर्मिनल VDD/2 वोल्टेज से जुड़ा है। op-amp अब अपने आउटपुट को उत्तेजना संकेत के विपरीत दिशा में समायोजित करने का प्रयास करेगा जैसे कि नकारात्मक टर्मिनल पर वोल्टेज VDD/2 के बराबर होगा। यह शरीर के माध्यम से करंट को धकेलने और खींचने की क्षमता पैदा करेगा।

op-amp के ऋणात्मक टर्मिनल से खींची गई धारा वस्तुतः शून्य है। इसलिए करंट सेंसिंग रेसिस्टर के माध्यम से सभी करंट को शरीर के माध्यम से प्रवाहित करना होता है। यह वह तंत्र है जो इस सेटअप को एक ट्रांस-चालन एम्पलीफायर (जिसे वोल्टेज नियंत्रित वर्तमान स्रोत, वीसीसीएस भी कहा जाता है) बनाता है।

op-amp केवल तभी करंट को बनाए रख सकता है जब शरीर का प्रतिबाधा बहुत अधिक न हो। अन्यथा op-amp आउटपुट केवल आपूर्ति वोल्टेज (0 या 5 V) पर अधिकतम होगा। अधिकतम वोल्टेज अवधि जिसे बनाए रखा जा सकता है वह है VDD/2 + Upeak (2.5+1.5V = 4V @ 5V आपूर्ति)। ऑप-एम्प के वोल्टेज मार्जिन को इस मान से घटाया जाना चाहिए, लेकिन अगर ऑप-एम्प में रेल-टू-रेल स्पेक्स हैं जो केवल एक छोटी राशि होगी। इसलिए op-amp द्वारा चलाई जा सकने वाली अधिकतम प्रतिबाधा है:

Z < (VDD/2 + Upeak) / Imax

(मेरे सेटअप में Z <4V/14 microAmps = 285 kOhms, इच्छा शरीर की प्रतिबाधा सीमा को कवर करने के लिए बहुत है)

रक्षक रोकनेवाला का शरीर (लगभग 100kOhms) की तुलना में बहुत बड़ा मूल्य (1-1.5 MOhms) होता है और सभी सामान्य ऑपरेशनों के लिए यह कोई ध्यान देने योग्य धारा नहीं खींचेगा और समानांतर कनेक्शन की बाधा शरीर के प्रतिबाधा पर हावी होती है। यदि शरीर की प्रतिबाधा बढ़नी चाहिए (जैसे पैड ढीले आ रहे हैं) तो करंट रेसिस्टर से होकर जा सकता है और ऑप-एम्प से अधिकतम होने से पैड में अप्रिय वोल्टेज नहीं पैदा होगा।

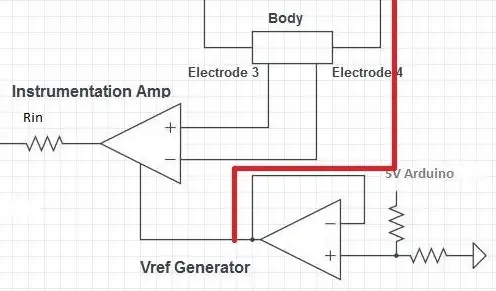

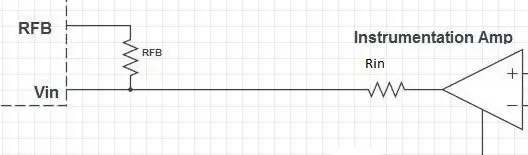

चरण 4: इंस्ट्रुमेंटेशन एम्पलीफायर

अगला चरण इंस्ट्रूमेंटेशन एम्पलीफायर (इन-एम्पी) है जो पूरे शरीर में वोल्टेज को मापता है। पूरे शरीर में वोल्टेज 0V के आसपास दोलन कर रहा है, लेकिन AD5933 को सकारात्मक सीमा में होने के लिए इनपुट वोल्टेज की आवश्यकता होती है। इन-एम्प इसलिए मापा वोल्टेज सिग्नल में वीडीडी / 2 के डीसी ऑफसेट को जोड़ता है।

VDD/2 संदर्भ एक वोल्टेज विभक्त द्वारा उत्पन्न होता है। किसी भी मूल्य अवरोधक का उपयोग तब तक किया जा सकता है जब तक वे समान हों। वोल्टेज विभक्त को वोल्टेज अनुयायी द्वारा शेष सर्किटरी के प्रतिबाधा से अलग किया जाता है। वोल्टेज फॉलोअर के आउटपुट को इन-एम्पी और ट्रांस-कंडक्टेंस एम्पलीफायर दोनों को अग्रेषित किया जा सकता है।

चरण 5: इनपुट चरण और अंशांकन

AD5933 के इनपुट चरण में नकारात्मक प्रतिक्रिया कॉन्फ़िगरेशन में एक op-amp शामिल है। दो प्रतिरोधक हैं: एक श्रृंखला में (रिन) और एक समानांतर (आरएफबी) में। op-amp का लाभ किसके द्वारा दिया जाता है

ए = - आरएफबी / रिन

इनपुट op-amp और in-amp (और PGA) के लाभ को यह सुनिश्चित करने की आवश्यकता है कि AD5933 के ADC में जाने वाला सिग्नल हमेशा 0V और VDD के भीतर हो।

(मैं एक यूनिटी गेन इन-एम्प और रेसिस्टर वैल्यू का उपयोग करता हूं जो लगभग ए = 0.5 देगा)

AD5933 के अंदर ADC वोल्टेज सिग्नल को डिजिटल सिग्नल में बदल देगा। 0V से VDD तक की वोल्टेज रेंज को डिजिटल रेंज 0-128 (2^7) में बदल दिया जाता है। (इस पर दस्तावेज़ीकरण स्पष्ट नहीं है लेकिन [1] में भूखंडों की एक करीबी परीक्षा और मेरी ओर से कुछ प्रयोग इसकी पुष्टि करते हैं।)

वास्तविक और काल्पनिक रजिस्टर में परिणाम सहेजे जाने से पहले डीएफटी मॉड्यूल के अंदर 256 (1024/4, देखें [1]) की एक और स्केलिंग है।

वोल्टेज सिग्नल का पालन करके AFE को ADC में गर्त में ले जाकर और पहले बताए गए पैमाने के कारकों का उपयोग करके लाभ-कारक का अनुमान लगाना संभव है:

g = (VDD * Rcurrent * Rin) / (256 * PGA * Upeak * RFB * 2^7)

कुछ अंशांकन अभी भी आवश्यक हो सकता है इसलिए कुछ प्रभावों के लिए खाते हैं जो इस गणितीय मॉडल का हिस्सा नहीं हैं, इसलिए कृपया प्रतिरोधों जैसे ज्ञात प्रतिबाधा के घटकों को मापकर वास्तविक लाभ मूल्य को मापें। (जी = जेड / पत्रिका, नीचे देखें)

प्रतिबाधा की गणना अब द्वारा की जा सकती है

जेड = जी * मैग

पत्रिका = sqrt(असली^2 + काल्पनिक^2)

PA = arctan2(वास्तविक, काल्पनिक) - डेल्टाPA

पीए को शायद कैलिब्रेट करने की जरूरत है और साथ ही AD5933 में आवृत्ति के एक समारोह के रूप में एक व्यवस्थित चरण-शिफ्ट है। डेल्टापीए शायद आवृत्ति का कुछ रैखिक कार्य होगा।

प्रतिरोध और प्रतिक्रिया की गणना अब द्वारा की जा सकती है

आर = जेड * कॉस (पीए)

एक्स = जेड * पाप (पीए)

सन्दर्भ:[1] लियोनिद मत्सिएव, "एडी५९३३ जैसे एकल-आवृत्ति डीएफटी डिटेक्टरों के आधार पर सिस्टम के प्रदर्शन और बहुमुखी प्रतिभा में सुधार", इलेक्ट्रॉनिक्स २०१५, ४, १-३४; डीओआई:10.3390/इलेक्ट्रॉनिक्स4010001

चरण 6: उन्नत सामग्री: वर्णक्रमीय रिसाव (डीसी)

AD5933 में हम जो संकेत डालते हैं, वह समय के एक समारोह के रूप में एक वोल्टेज/करंट है, लेकिन हमारी मुख्य रुचि आवृत्ति के एक समारोह के रूप में प्रतिबाधा है। टाइम-डोमेन और फ़्रीक्वेंसी-डोमेन के बीच कनवर्ट करने के लिए हमें टाइम-डोमेन सिग्नल का फूरियर ट्रांसफ़ॉर्म लेना होगा। AD5933 में एक अंतर्निहित असतत फूरियर रूपांतरण (DFT) मॉड्यूल है। कम आवृत्तियों पर (लगभग 10 kHz से कम) DFT में निर्माण अलियासिंग और वर्णक्रमीय रिसाव से प्रभावित होता है। [१] में वह वर्णक्रमीय रिसाव को ठीक करने के तरीके के गणित के माध्यम से जाता है। इसका सार स्वीप में प्रत्येक आवृत्ति चरण के लिए पांच (प्लस दो) स्थिरांक की गणना करना है। यह आसानी से किया जा सकता है उदा। सॉफ्टवेयर में Arduino द्वारा।

रिसाव दो रूपों में आता है: एक डीसी रिसाव जो प्रकृति में योगात्मक है और एक एसी रिसाव जो प्रकृति में गुणक है।

डीसी रिसाव इस तथ्य से उपजा है कि एडीसी पर वोल्टेज संकेत 0V के आसपास नहीं बल्कि VDD/2 के आसपास दोलन कर रहा है। VDD/2 का DC स्तर लगभग 64 के डिजिटल DC रीडिंग के अनुरूप होना चाहिए ([1] में निर्दिष्ट डेल्टा)।

डीसी वर्णक्रमीय रिसाव को ठीक करने के लिए कदम:

1) वर्तमान आवृत्ति के लिए लिफाफा-कारक ई की गणना करें।

2) दो लाभ कारक जीआई (वास्तविक) और जीक्यू (काल्पनिक) की गणना करें

3) वास्तविक रजिस्टर के मूल्य से डेल्टा * जीआई घटाएं और काल्पनिक रजिस्टर के मूल्य से डेल्टा * जीक्यू घटाएं

सन्दर्भ:

[१] लियोनिद मत्सिएव, "पर आधारित सिस्टम के प्रदर्शन और बहुमुखी प्रतिभा में सुधार"

एकल-आवृत्ति DFT डिटेक्टर जैसे AD5933 , इलेक्ट्रॉनिक्स 2015, 4, 1-34; doi: 10.3390/इलेक्ट्रॉनिक्स4010001

[२] कोनराड चाबोव्स्की, टोमाज़ पियासेकी, आंद्रेज़ डिज़िएर्का, करोल निट्स्च, "एडी ५९३३ इंटीग्रेटेड सर्किट पर आधारित सिंपल वाइड फ़्रीक्वेंसी रेंज इम्पीडेंस मीटर", मेट्रोल। उपाय। सिस्ट।, वॉल्यूम। XXII (2015), नंबर 1, पीपी। 13-24।

चरण 7: उन्नत सामग्री: वर्णक्रमीय रिसाव (एसी)

डीसी रिसाव की तरह एसी रिसाव को गणितीय रूप से ठीक किया जा सकता है। [१] में प्रतिरोध और प्रतिक्रिया को क्रमशः A*cos(phi) और A*sin(phi) कहा जाता है, जहां A प्रतिबाधा के परिमाण से मेल खाता है और phi चरण कोण (PA) से मेल खाता है।

एसी वर्णक्रमीय रिसाव को ठीक करने के लिए कदम:

1) वर्तमान आवृत्ति के लिए लिफाफा-कारक ई (डीसी के लिए समान नहीं) की गणना करें।

2) तीन कारकों ए, बी, और डी की गणना करें। (उच्च आवृत्तियों पर लगभग मान: ए = डी = 256 और बी = 0)

3) प्रतिरोध (Acos(phi)) और प्रतिक्रिया (Asin(phi)) की गणना अब डिजिटल इकाइयों में की जा सकती है

सन्दर्भ:[1] लियोनिद मत्सिएव, "एडी५९३३ जैसे सिंगल-फ़्रीक्वेंसी डीएफटी डिटेक्टरों के आधार पर सिस्टम के प्रदर्शन और बहुमुखी प्रतिभा में सुधार", इलेक्ट्रॉनिक्स २०१५, ४, १-३४; डीओआई:10.3390/इलेक्ट्रॉनिक्स4010001

[२] कोनराड चाबोव्स्की, टोमाज़ पियासेकी, आंद्रेज़ डिज़िएर्का, करोल निट्स्च, "एडी ५९३३ इंटीग्रेटेड सर्किट पर आधारित सिंपल वाइड फ़्रीक्वेंसी रेंज इम्पीडेंस मीटर", मेट्रोल। उपाय। सिस्ट।, वॉल्यूम। XXII (2015), नंबर 1, पीपी। 13-24।

चरण 8: उन्नत सामग्री: सैद्धांतिक लाभ-कारक

डीएफटी के गणितीय मॉडलिंग को देखते हुए पूरे एएफई को गणितीय रूप से मॉडल करना भी संभव होना चाहिए। गणितीय रूप से वोल्टेज सिग्नल को एक निश्चित आवृत्ति के साथ साइन फ़ंक्शन द्वारा वर्णित किया जा सकता है, एक डीसी ऑफ़सेट और एक एसी दोलन एक शिखर आयाम के साथ। आवृत्ति चरण के दौरान आवृत्ति नहीं बदलती है। चूंकि लाभ-कारक केवल प्रतिबाधा के परिमाण को बदलता है और पीए को नहीं, हम यहां सिग्नल पर प्रेरित किसी भी चरण बदलाव से चिंतित नहीं होंगे।

यहाँ वोल्टेज सिग्नल का संक्षिप्त सारांश दिया गया है क्योंकि यह AFE के माध्यम से फैलता है:

1) पुन: पूर्वाग्रह चरण के बाद एसी आयाम अभी भी उपक = 1.5 वी (1 वी @ वीडीडी = 3.3 वी) है और डीसी ऑफ़सेट को वीडीडी/2 में बदल दिया गया है।

2) करंट सेंसिंग रेसिस्टर में वोल्टेज पिछले चरण की तरह ही स्थिर होता है …

3) … लेकिन op-amp के सीसॉ-वोल्टेज के कारण AC दोलनों का आकार Z* Upeak/Rcurrent होता है। (डीसी ऑफ़सेट को वीडीडी/2 के ऑप-एम्प्स संदर्भ वोल्टेज द्वारा रद्द कर दिया गया है - सीसॉ का धुरी बिंदु - और सर्किट के इस हिस्से में एक पुण्य जमीन बन जाता है)

4) एकता इन-एम्पी VDD/2 के DC ऑफ़सेट को वापस अंदर जोड़ता है और AD5933 के इनपुट चरण में सिग्नल को अग्रेषित करता है

5) इनपुट चरण में op-amp में A=-RFB/Rin का लाभ होता है और इसलिए AC आयाम (Z*Upeak/Rcurrent)*(RFB/Rin) बन जाता है।

6) एडीसी के ठीक पहले एक प्रोग्रामेबल गेन एम्पलीफायर (पीजीए) होता है जिसमें दो सेटिंग्स 1 या 5 का लाभ होता है। एडीसी पर वोल्टेज सिग्नल इसलिए बन जाता है: पीजीए * (जेड * अपेक/रकुरेंट) * (आरएफबी/रिन)

एडीसी 12 बिट सटीकता के साथ v(t) सिग्नल को डिजिटल सिग्नल x(t) = u(t) / VDD * 2^7 में परिवर्तित करता है।

परिमाण ए प्रतिबाधा जेड से लाभ कारक, के द्वारा ए = के * जेड के रूप में जुड़ा हुआ है और इसका लगभग के = पीजीए * उपक * आरएफबी * 2^7 / (वीडीडी * रकरंट * रिन) का लगभग मूल्य है।

यदि आप g = 1 / k और Z = g * A के बजाय लाभ-कारक के साथ काम करना पसंद करते हैं।

चरण 9: उन्नत सामग्री: पीए शिफ्ट

[2] में वे आवृत्ति के एक फलन के रूप में PA में एक व्यवस्थित बदलाव पाते हैं। यह डीएसी के बीच एक समय की देरी के कारण है जहां उत्तेजना संकेत उत्पन्न होता है और डीएफटी जहां आने वाले सिग्नल को आउटगोइंग सिग्नल के साथ जटिल करने की आवश्यकता होती है।

बदलाव को घड़ी-चक्रों की संख्या की विशेषता है जो AD5933 में आंतरिक रूप से DAC और DFT के बीच संकेत देरी है।

सन्दर्भ:[1] लियोनिद मत्सिएव, "एडी५९३३ जैसे एकल-आवृत्ति डीएफटी डिटेक्टरों के आधार पर सिस्टम के प्रदर्शन और बहुमुखी प्रतिभा में सुधार", इलेक्ट्रॉनिक्स २०१५, ४, १-३४; डीओआई:10.3390/इलेक्ट्रॉनिक्स4010001

[२] कोनराड चाबोव्स्की, टोमाज़ पियासेकी, आंद्रेज़ डिज़िएर्का, करोल निट्स्च, "एडी ५९३३ इंटीग्रेटेड सर्किट पर आधारित सिंपल वाइड फ़्रीक्वेंसी रेंज इम्पीडेंस मीटर", मेट्रोल। उपाय। सिस्ट।, वॉल्यूम। XXII (2015), नंबर 1, पीपी। 13-24।

सिफारिश की:

Ubidots और Google-शीट्स का उपयोग करके अस्थायी/आर्द्रता डेटा विश्लेषण: ६ चरण

Ubidots और Google-Sheets का उपयोग करके अस्थायी/आर्द्रता डेटा विश्लेषण: इस ट्यूटोरियल में, हम तापमान और आर्द्रता सेंसर का उपयोग करके विभिन्न तापमान और आर्द्रता डेटा को मापेंगे। आप यह भी सीखेंगे कि इस डेटा को यूबीडॉट्स को कैसे भेजा जाए। ताकि आप अलग-अलग एप्लिकेशन के लिए कहीं से भी इसका विश्लेषण कर सकें। प्रेषक द्वारा भी

ईसीजी लॉगर - दीर्घकालिक डेटा अधिग्रहण और विश्लेषण के लिए पहनने योग्य कार्डिएक मॉनिटर: 3 चरण

ईसीजी लॉगर - लंबी अवधि के डेटा अधिग्रहण और विश्लेषण के लिए एक पहनने योग्य कार्डिएक मॉनिटर: पहली रिलीज: अक्टूबर 2017नवीनतम संस्करण: 1.6.0स्थिति: स्थिर कठिनाई: उच्च शर्त: Arduino, प्रोग्रामिंग, हार्डवेयर बिल्डिंग अद्वितीय भंडार: एसएफ (नीचे लिंक देखें) समर्थन: केवल फोरम, कोई पीएमईसीजी लॉगर लंबे समय तक पहनने योग्य कार्डिएक मॉनिटर नहीं है

भाग 1. ThinkBioT स्वायत्त जैव-ध्वनिक सेंसर हार्डवेयर बिल्ड: 13 चरण

भाग 1. ThinkBioT स्वायत्त जैव-ध्वनिक सेंसर हार्डवेयर बिल्ड: ThinkBioT का उद्देश्य डेटा संग्रह, पूर्व-प्रसंस्करण, डेटा ट्रांसमिशन और विज़ुअलाइज़ेशन कार्यों को सक्षम करने के लिए डेटा संग्रह, पूर्व-प्रसंस्करण, डेटा ट्रांसमिशन और विज़ुअलाइज़ेशन कार्यों को संभालने के द्वारा, आगे के शोध का समर्थन करने के लिए एक तकनीकी रीढ़ के रूप में डिज़ाइन किया गया एक सॉफ़्टवेयर और हार्डवेयर ढांचा प्रदान करना है। शोधकर्ता

रास्पबेरी पाई के साथ ट्विटर भावना विश्लेषण: 3 चरण (चित्रों के साथ)

रास्पबेरी पाई के साथ ट्विटर सेंटीमेंट एनालिसिस: सेंटीमेंट एनालिसिस क्या है, और आपको इसकी परवाह क्यों करनी चाहिए? सेंटीमेंट एनालिसिस शब्दों की एक श्रृंखला के पीछे भावनात्मक स्वर को निर्धारित करने की प्रक्रिया है, जिसका उपयोग व्यक्त किए गए दृष्टिकोण, राय और भावनाओं की समझ हासिल करने के लिए किया जाता है। एक के भीतर

जैव निगरानी: 8 कदम (चित्रों के साथ)

जैव निगरानी: सभी को नमस्कार, एक छात्र परियोजना के संदर्भ में, हमें सभी प्रक्रियाओं का वर्णन करने वाला एक लेख प्रकाशित करने के लिए कहा गया था। फिर हम आपको पेश करेंगे कि हमारी जैव निगरानी प्रणाली कैसे काम करती है। यह एक पोर्टेबल डिवाइस है जो निगरानी की अनुमति देता है नमी