विषयसूची:

- चरण 1: निर्दिष्टीकरण

- चरण 2: पीआईसी का अवलोकन

- चरण 3: आरटीएल डिजाइन और कार्यान्वयन

- चरण 4: महत्वपूर्ण नोट्स और संलग्न फ़ाइलें

वीडियो: VHDL में प्रोग्रामेबल इंटरप्ट कंट्रोलर का डिज़ाइन: 4 चरण

2024 लेखक: John Day | [email protected]. अंतिम बार संशोधित: 2024-01-30 09:20

इस ब्लॉग पर मुझे जिस तरह की प्रतिक्रियाएं मिल रही हैं, उससे मैं अभिभूत हूं। मेरे ब्लॉग पर आने और मुझे अपने ज्ञान को आपके साथ साझा करने के लिए प्रेरित करने के लिए धन्यवाद दोस्तों। इस बार, मैं एक और दिलचस्प मॉड्यूल का डिज़ाइन प्रस्तुत करने जा रहा हूँ जो हम सभी एसओसी में देखते हैं - इंटरप्ट कंट्रोलर।

हम एक सरल लेकिन शक्तिशाली प्रोग्रामेबल इंटरप्ट कंट्रोलर डिजाइन करेंगे। यह पूरी तरह से विन्यास योग्य और पैरामीटरयुक्त डिजाइन है जो सभी प्लेटफार्मों पर पोर्टेबल है। मैंने इसे NVIC, 8259a, RISC-V PLIC, Microblaze's INTC आदि जैसे कुछ लोकप्रिय इंटरप्ट कंट्रोलर आर्किटेक्चर पर बहुत कुछ पढ़ने के बाद डिज़ाइन किया है। आशा है कि आप लोगों को यह ब्लॉग मददगार लगेगा और आपको एक प्रोसेसर द्वारा इंटरप्ट को कैसे हैंडल किया जाता है, इस पर एक स्वाद प्राप्त करने में मदद करता है। एक इंटरप्ट कंट्रोलर की मदद से।

चरण 1: निर्दिष्टीकरण

आईपी के विनिर्देश निम्नलिखित हैं:

- AHB3-लाइट इंटरफ़ेस।

-

स्थिर रूप से विन्यास योग्य पैरामीटर:

- बाहरी व्यवधान स्रोतों की संख्या; 63 इंटरप्ट तक का समर्थन करता है।

- प्राथमिकता स्तरों की संख्या; 63 स्तरों तक का समर्थन करता है।

- घोंसले के स्तर की संख्या; घोंसले के शिकार के 8 स्तर तक का समर्थन करता है। मैं

- बस की चौड़ाई; 32 या 64.

- वैश्विक और स्थानीय रूप से नकाबपोश व्यवधान।

- प्रत्येक व्यवधान के लिए गतिशील रूप से विन्यास योग्य प्राथमिकता स्तर।

- ऑपरेशन के दो तरीके - फुली नेस्टेड मोड और इक्वल प्रायोरिटी मोड।

- सक्रिय-उच्च स्तरीय संवेदनशील व्यवधानों का समर्थन करता है।

आरआईएससी-वी पीएलआईसी विनिर्देशों से प्रेरित इंटरप्ट हैंडशेकिंग तंत्र डिजाइन में उपयोग किया जाता है।

इंटरप्ट प्री-एम्प्शन 8259a. से प्रेरित है

अन्य पढ़े: माइक्रोब्लेज़ आईएनटीसी, एनवीआईसी

चरण 2: पीआईसी का अवलोकन

प्रोग्रामेबल इंटरप्ट कंट्रोलर (PIC) बाहरी पेरिफेरल्स से कई इंटरप्ट प्राप्त करता है और उन्हें सिंगल इंटरप्ट आउटपुट में टारगेट प्रोसेसर कोर में मिला देता है।

PIC को नियंत्रण और स्थिति रजिस्टरों के माध्यम से नियंत्रित किया जाता है। सभी PIC रजिस्टर मेमोरी मैप किए जाते हैं, और AHB3-Lite बस इंटरफेस के माध्यम से एक्सेस किए जाते हैं।

रजिस्टर बैंक में कॉन्फ़िगरेशन रजिस्टर, सक्षम रजिस्टर, लंबित रजिस्टर, इन-सर्विस रजिस्टर, प्राथमिकता रजिस्टर और आईडी रजिस्टर होते हैं, जो इंटरप्ट कंट्रोलर में विशिष्ट होते हैं।

कॉन्फ़िगरेशन रजिस्टर का उपयोग PIC के संचालन के तरीके को सेट करने के लिए किया जाता है। यह पूरी तरह से नेस्टेड मोड या समान प्राथमिकता मोड में काम कर सकता है।

प्रत्येक रुकावट को प्राथमिकता दी जा सकती है और व्यक्तिगत रूप से नकाबपोश किया जा सकता है। सभी व्यवधानों की वैश्विक मास्किंग भी समर्थित है।

लंबित इंटरप्ट की प्राथमिकताओं को हल करने के लिए रजिस्टर बैंक प्राथमिकता रिज़ॉल्वर और बीटीसी (बाइनरी-ट्री-तुलनित्र) के साथ बातचीत करता है और तदनुसार प्रोसेसर को इंटरप्ट करता है। आईडी रजिस्टर में उच्चतम प्राथमिकता लंबित रुकावट की आईडी होती है।

चरण 3: आरटीएल डिजाइन और कार्यान्वयन

PIC का डिज़ाइन प्राथमिकताओं को हल करने की विलंबता को कम करने पर जोर देता है, जो कि डिज़ाइन का सबसे महत्वपूर्ण हिस्सा है। चूंकि डिज़ाइन एकल घड़ी चक्र में प्राथमिकताओं को हल करता है, इसलिए Log2 जटिलता वाले स्रोतों की संख्या में वृद्धि के साथ प्रदर्शन में गिरावट आती है।

डिजाइन को सफलतापूर्वक कार्यान्वित किया गया था और Artix-7 FPGAs पर निम्नलिखित आवृत्तियों तक समय सत्यापित किया गया था।

- 15 स्रोतों तक: 100 मेगाहर्ट्ज

- 63 स्रोतों तक: 50 मेगाहर्ट्ज

अकेले पीआईसी द्वारा जोड़ा गया इंटरप्ट लेटेंसी 3 घड़ी चक्र है (प्रोसेसर के संदर्भ स्विच समय और पहले आईएसआर निर्देश लाने के समय को छोड़कर)।

चरण 4: महत्वपूर्ण नोट्स और संलग्न फ़ाइलें

महत्वपूर्ण लेख:

- यदि AHB3-Lite इंटरफ़ेस अवांछित है, तो आप शीर्ष मॉड्यूल को बदल सकते हैं और PIC के कंकाल डिज़ाइन का उपयोग कर सकते हैं। हालांकि प्रदान की गई परीक्षण बेंच एएचबी 3-लाइट इंटरफेस के साथ आईपी के लिए है।

- PIC IP v1.0 पूरी तरह से पोर्टेबल, बेयर RTL डिज़ाइन है।

- दोनों मोड पर काम करने के लिए कार्यात्मक रूप से सत्यापित।

संलग्न फाइल:

- वीएचडीएल में डिजाइन कोड और टेस्टबेंच।

- पूर्ण आईपी प्रलेखन।

यह एक ओपन-सोर्स डिज़ाइन है … बेझिझक उपयोग करें …

किसी भी प्रश्न के लिए, किसी भी समय:

मीतू राजो

सिफारिश की:

फ़्लिक में गेम डिज़ाइन ५ चरणों में: ५ चरण

5 चरणों में फ़्लिक में गेम डिज़ाइन: फ़्लिक गेम बनाने का एक बहुत ही सरल तरीका है, विशेष रूप से एक पहेली, दृश्य उपन्यास, या साहसिक खेल जैसा कुछ

VHDL में एक साधारण फोर-वे सेट एसोसिएटिव कैश कंट्रोलर का डिज़ाइन: 4 चरण

VHDL में एक साधारण फोर-वे सेट एसोसिएटिव कैश कंट्रोलर का डिज़ाइन: मेरे पिछले निर्देश में, हमने देखा कि एक साधारण डायरेक्ट मैप किए गए कैशे कंट्रोलर को कैसे डिज़ाइन किया जाए। इस बार हम एक कदम आगे बढ़ते हैं। हम एक साधारण चार-तरफा सेट सहयोगी कैश नियंत्रक तैयार करेंगे। लाभ ? कम छूट दर, लेकिन प्रदर्शन की कीमत पर

VHDL में एक साधारण कैश नियंत्रक का डिज़ाइन: 4 चरण

VHDL में एक साधारण कैश नियंत्रक का डिज़ाइन: मैं यह निर्देश योग्य लिख रहा हूँ, क्योंकि मुझे कुछ संदर्भ VHDL कोड सीखने और कैशे नियंत्रक को डिज़ाइन करना शुरू करने में थोड़ा मुश्किल लगा। इसलिए मैंने स्क्रैच से खुद को कैशे कंट्रोलर डिज़ाइन किया, और FPGA पर इसका सफलतापूर्वक परीक्षण किया। मेरे पास प

VHDL में I2C मास्टर का डिज़ाइन: 5 चरण

VHDL में I2C मास्टर का डिज़ाइन: इस निर्देश में, VHDL में एक साधारण I2C मास्टर को डिज़ाइन करने पर चर्चा की गई है। नोट: पूर्ण छवि देखने के लिए प्रत्येक छवि पर क्लिक करें

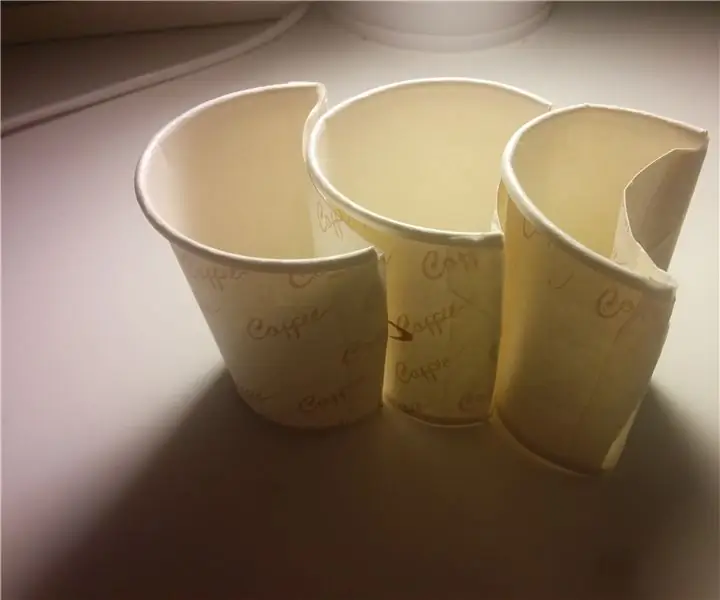

डिज़ाइन थिंकिंग मेथड्स के साथ एक कार्डबोर्ड कप डिज़ाइन करें: 7 चरण

डिज़ाइन थिंकिंग मेथड्स के साथ एक कार्डबोर्ड कप डिज़ाइन करें: हैलो, कार्डबोर्ड कप जिसे डिज़ाइन थिंकिंग विधियों के अनुसार डिज़ाइन किया गया है, यहाँ। कृपया इसे देखें और एक टिप्पणी करें। मैं आपकी टिप्पणियों के साथ अपनी परियोजना में सुधार करूंगा