विषयसूची:

- चरण 1: ट्रांसमीटर के लिए Zynq प्रोग्रामेबल लॉजिक कॉन्फ़िगर करें

- चरण 2: रिसीवर के लिए Zynq प्रोग्रामेबल लॉजिक को कॉन्फ़िगर करें

- चरण 3: सेटअप VDMA ड्राइवर

- चरण 4: सेटअप नैनोराउटर नेटवर्क

- चरण 5: ईथरनेट के माध्यम से डेटा ट्रांसमिशन के लिए Zynq प्रोसेसिंग सिस्टम सेटअप करें

- चरण 6: ईथरनेट के माध्यम से डेटा रिसेप्शन के लिए Zynq प्रोसेसिंग सिस्टम सेटअप करें

- चरण 7: अपने Zybo बोर्डों को HDMI स्रोत और HDMI सिंक से कनेक्ट करें

- चरण 8: सुधार के लिए वैकल्पिक विचार

- चरण 9: अभिगम्यता

वीडियो: WIDI - Zybo (Zynq डेवलपमेंट बोर्ड) का उपयोग कर वायरलेस एचडीएमआई: 9 कदम (चित्रों के साथ)

2024 लेखक: John Day | [email protected]. अंतिम बार संशोधित: 2024-01-30 09:22

क्या आपने कभी यह चाहा है कि आप अपने टीवी को पीसी या लैपटॉप से बाहरी मॉनिटर के रूप में कनेक्ट कर सकें, लेकिन क्या आप उन सभी अजीब डोरियों को रास्ते में नहीं लाना चाहते थे? यदि हां, तो यह ट्यूटोरियल सिर्फ आपके लिए है! जबकि कुछ उत्पाद हैं जो इस लक्ष्य को प्राप्त करते हैं, एक DIY परियोजना अधिक संतोषजनक और संभावित रूप से सस्ता है।

यह अवधारणा क्रोमकास्ट जैसे उत्पादों से अलग है, क्योंकि इसका उद्देश्य स्ट्रीमिंग डिवाइस होने के बजाय मॉनिटर से कनेक्ट होने वाले एचडीएमआई कॉर्ड की जगह लेना है।

हमारा प्रोजेक्ट कैलिफ़ोर्निया स्टेट पॉलिटेक्निक यूनिवर्सिटी, सैन लुइस ओबिस्पो में रीयल टाइम ऑपरेटिंग सिस्टम कोर्स के लिए अंतिम प्रोजेक्ट के रूप में बनाया गया था।

परियोजना का लक्ष्य दो डिजिलेंट ज़ीबो बोर्डों का उपयोग एचडीएमआई ट्रांसमीटर डिवाइस (पीसी, ब्लू-रे, आदि) के बीच एक एचडीएमआई रिसीविंग डिवाइस (डेस्कटॉप मॉनिटर, प्रोजेक्टर, टीवी, आदि) के बीच वायरलेस संचार इंटरफेस के रूप में कार्य करने के लिए करना है।

एक Digilent Zybo एचडीएमआई के माध्यम से ट्रांसमिटिंग डिवाइस से जुड़ा होगा, और दूसरा एचडीएमआई के माध्यम से रिसीविंग डिवाइस से जुड़ा होगा।

वायरलेस संचार ट्रांसमीटर और रिसीवर को समर्पित एक वायरलेस लोकल एरिया नेटवर्क का उपयोग करके किया जाएगा, बिना होम राउटर या ऐसे अन्य डिवाइस के माध्यम से रूट किए बिना। इस परियोजना के लिए उपयोग किया जाने वाला वायरलेस मॉड्यूल tplink wr802n नैनोराउटर है, जिसमें से एक नेटवर्क स्थापित करने के लिए एक्सेस प्वाइंट के रूप में काम करता है और दूसरा नेटवर्क से कनेक्ट करने के लिए क्लाइंट के रूप में काम करता है। प्रत्येक नैनोराउटर को ईथरनेट केबल के माध्यम से या तो Zybo बोर्ड से जोड़ा जाएगा। इन राउटर से कनेक्ट होने पर, डिवाइस टीसीपी के माध्यम से संचार करेंगे जैसे कि वे एक एकल ईथरनेट केबल से जुड़े थे (मतलब कनेक्शन स्थापित करने के लिए आवश्यक एकमात्र कॉन्फ़िगरेशन क्लाइंट का आईपी पता है)।

जबकि परियोजना का लक्ष्य 1080x720 वीडियो @ 60 हर्ट्ज की एक धारा को सुविधाजनक बनाना था, यह वायरलेस नेटवर्क में बैंडविड्थ सीमाओं और भेजने के लिए आवश्यक डेटा को कम करने के लिए वास्तविक समय वीडियो संपीड़न की कमी के कारण प्राप्त करने योग्य नहीं था। इसके बजाय, यह परियोजना इस लक्ष्य को प्राप्त करने के लिए भविष्य के विकास के लिए रूपरेखा के रूप में कार्य करती है, क्योंकि इसमें एचडीएमआई डेटा को ठीक से स्ट्रीम करने के लिए फ्रेम दर में गंभीर रूप से प्रतिबंधित सीमाएं हैं।

परियोजना आवश्यकताएँ:

2x Digilent Zybo Development Boards (कम से कम एक HDMI पोर्ट होना चाहिए)

2x एचडीएमआई केबल

2x माइक्रोयूएसबी केबल (विकास के लिए ज़ीबो को पीसी से जोड़ने के लिए)

2x tplink wr802n nanorouters (adtl. 2x microusb और वॉल आउटलेट पावर एडेप्टर सहित)

2x ईथरनेट केबल

***नोट: यह ट्यूटोरियल विवाडो डिज़ाइन सूट से परिचित है और एक नया प्रोजेक्ट और ब्लॉक डिज़ाइन बनाने का अनुभव है।***

चरण 1: ट्रांसमीटर के लिए Zynq प्रोग्रामेबल लॉजिक कॉन्फ़िगर करें

ट्रांसमीटर के प्रोग्रामेबल लॉजिक को विकसित करने के लिए हमारा दृष्टिकोण दो वीडियो डायरेक्ट मेमोरी एक्सेस (वीडीएमए) ब्लॉकों का उपयोग करके मॉनिटर करने के लिए पीसी से एचडीएमआई-टू-एचडीएमआई पास-थ्रू करना था, एक लिखने के लिए और एक पढ़ने के लिए।

दोनों को फ्री-रनिंग, 3 फ्रेम-बफर मोड (0-1-2) के लिए चुना गया है। चूंकि वीडियो कोर 60 फ्रेम प्रति सेकंड के लिए अनुकूलित है, इसका मतलब है कि वीडीएमए इस क्रम में प्रत्येक 16.67 एमएस में एक नया फ्रेम लिखेगा या पढ़ेगा: 0, 1, 2, 0, 1, 2, 0, 1, 2. प्रत्येक फ़्रेम के लिए DDR मेमोरी स्थान दो VDMA के लिए भिन्न होते हैं क्योंकि वे अब एक दूसरे के साथ सिंक्रनाइज़ नहीं होते हैं। इसके बजाय, 60 हर्ट्ज के लिए कॉन्फ़िगर किया गया एक हार्डवेयर टाइमर (TTC1), दो मेमोरी स्थानों के बीच डेटा की गति को सिंक्रनाइज़ करने के लिए उपयोग किया जाता है।

ऊपर की छवि 3 फ्रेम दिखाती है, उनके आयाम और प्रत्येक के लिए आवश्यक मेमोरी की मात्रा (फ्रेम के दाईं ओर)। अगर हम इन मेमोरी लोकेशन को वीडीएमए लिखते हैं, तो हम इस सेट से परे रीड वीडीएमए मेमोरी लोकेशन असाइन कर सकते हैं, मान लीजिए कि 0x0B000000 से शुरू होता है। प्रत्येक फ्रेम 1280*720 पिक्सल से बना है और प्रत्येक पिक्सेल कुल 24 बिट्स के लिए लाल, हरे और नीले रंग के 8 बिट्स से बना है। इसका मतलब है कि एक फ्रेम 1280*720*3 बाइट्स (2.76 एमबी) से बना है।

टाइमर के अंदर IRQ, जिसे VDMA ड्राइवर सेटअप में वर्णित किया गया है, दो VMDA मेमोरी स्थानों के बीच डेटा कॉपी करने का काम संभालेगा। वीडीएमए वर्तमान फ्रेम के लिए एक सूचक प्रदान करता है जिसे लिखा या पढ़ा जा रहा है। फ़्रेम को एक विशेष ग्रे कोड द्वारा दर्शाया जाता है, जिसे सॉफ़्टवेयर में परिवर्तित किया जाता है। 3 फ्रेम-बफर कॉन्फ़िगरेशन के लिए ग्रे कोड परिभाषाएँ परिशिष्ट C में AXI VDMA उत्पाद मार्गदर्शिका में पाई जा सकती हैं।

यह हमें वर्तमान में लिखे जा रहे फ्रेम से पढ़े बिना स्मृति में लिखी जा रही सामग्री को कॉपी करने की अनुमति देता है।

***ध्यान दें कि वायरलेस नेटवर्क पर डेटा भेजते समय रीड वीडीएमए का उपयोग नहीं किया जाता है। इसका एकमात्र उद्देश्य वीएमडीए लिखने से स्मृति की प्रतिलिपि बनाने के उचित संचालन को सत्यापित करना है। पढ़ा हुआ VMDA अक्षम किया जाना चाहिए।***

ट्रांसमीटर डिजाइन ब्लॉक बनाने के चरण यहां दिए गए हैं:

- एक नया प्रोजेक्ट बनाते समय, प्रोजेक्ट को एक चिप या बोर्ड असाइन करना एक अच्छा विचार है। यह लिंक बताता है कि विवाडो निर्देशिका में नई बोर्ड फ़ाइलों को कैसे जोड़ा जाए और सही बोर्ड को अपने प्रोजेक्ट से कैसे जोड़ा जाए। प्रोसेसिंग सिस्टम ब्लॉक को जोड़ने और हार्डवेयर से सॉफ्टवेयर (एसडीके साइड) में संक्रमण करते समय यह काम आएगा।

-

निम्नलिखित ब्लॉक जोड़ें:

- डीवीआई२आरजीबी

- Axi4-स्ट्रीम में वीडियो

- समय नियंत्रक

- axi4-स्ट्रीम vid आउट करने के लिए

- आरजीबी2डीवीआई

- एक्सी वीडीएमए x2

- AXI GPIO x2

- घड़ी जादूगर

- लगातार

- Zynq प्रोसेसिंग सिस्टम

- प्रोसेसिंग सिस्टम जोड़ते समय, ऊपर हरे रंग के बार से "रन ब्लॉक ऑटोमेशन" पर क्लिक करें और सुनिश्चित करें कि "बोर्ड प्रीसेट लागू करें" विकल्प चुना गया है। बाकी सब कुछ डिफ़ॉल्ट छोड़ दें।

- प्रत्येक ब्लॉक कॉन्फ़िगरेशन विंडो की छवियां ऊपर की छवियों में पाई जा सकती हैं। यदि आप किसी विशेष विंडो के लिए कोई छवि नहीं देखते हैं, तो इसे डिफ़ॉल्ट के रूप में छोड़ दें।

-

Zynq प्रोसेसिंग सिस्टम को कॉन्फ़िगर करना शुरू करें:

- PS-PL कॉन्फ़िगरेशन में AXI नॉन सिक्योर GP Master AXI को सक्षम करें, M AXI GP0 इंटरफ़ेस को सक्षम करें

- PS-PL कॉन्फ़िगरेशन में HP स्लेव AXI इंटरफ़ेस, HP0 और HP1 दोनों को सक्षम करें

- MIO कॉन्फ़िगरेशन में सुनिश्चित करें कि I/O पेरिफेरल्स के तहत ENET0 सक्षम है, फिर एप्लिकेशन प्रोसेसर यूनिट, Timer0 सक्षम करें

- क्लॉक कॉन्फ़िगरेशन PL फैब्रिक क्लॉक में, FCLK_CLK0 को सक्षम करें और 100 मेगाहर्ट्ज पर सेट करें।

- ओके पर क्लिक करें

- "रन कनेक्शन ऑटोमेशन" पर क्लिक करने से पहले, वीडियो ब्लॉक को कनेक्ट करना सुनिश्चित करें जैसा कि ऊपर TX ब्लॉक डिज़ाइन छवि में देखा गया है। आप स्थिरांक का नाम बदलकर VDD करना चाहेंगे और मान को 1 पर सेट करना चाहेंगे। तदनुसार वीडियो ब्लॉक कनेक्ट करें।

- rgb2dvi और dvi2rgb ब्लॉक पर HDMI TMDS घड़ी और डेटा पिन बाहरी बनाएं

- हॉट प्लग डिटेक्ट सिग्नल (एचपीडी) के लिए एक इनपुट और आउटपुट पोर्ट बनाएं और उन्हें एक साथ कनेक्ट करें, इन्हें बाधाओं फ़ाइल में परिभाषित किया गया है

-

पिक्सेल घड़ी TMDS_Clk_p से पुनर्प्राप्त की जाती है, जो कि बाधा फ़ाइल में बनाई गई है। यह 720p रेजोल्यूशन के अनुसार 74.25 मेगाहर्ट्ज होगा। पिक्सेल घड़ी (dvi2rgb ब्लॉक से) को निम्नलिखित पिनों से जोड़ना महत्वपूर्ण है:

- vid_io_in_clk (अक्ष स्ट्रीम ब्लॉक में vid)

- vid_io_out_clk (अक्ष स्ट्रीम से vid आउट ब्लॉक)

- क्लर्क (समय नियंत्रक)

- पिक्सेलक्लक (आरजीबी2डीवीआई)

- ***नोट: वर्तमान में, पिक्सेल क्लॉक रिकवरी को सक्रिय करने के लिए, एचडीएमआई आरएक्स और टीएक्स कनेक्टर को एक सक्रिय स्रोत / सिंक में प्लग किया जाना चाहिए। इसका एक तरीका यह है कि वीडियो rx और tx ब्लॉक को अलग-अलग क्लॉक डोमेन में अलग किया जाए (दूसरे शब्दों में, tx ब्लॉक को फीड करने के लिए एक नई 74.25 MHz घड़ी जेनरेट करें)।***

- अगला क्लॉक विजार्ड सेट करें ताकि आपके पास 100 मेगाहर्ट्ज इनपुट (ग्लोबल बफर सोर्स) और 3 आउटपुट क्लॉक @ 50 मेगाहर्ट्ज (एएक्सआई-लाइट क्लॉक), 150 मेगाहर्ट्ज (एएक्सआई 4-स्ट्रीम क्लॉक), 200 मेगाहर्ट्ज (डीवीआई2आरजीबी रेफक्लक पिन) हो।

- FCLK_CLK0 प्रोसेसिंग सिस्टम पिन को क्लॉक विजार्ड इनपुट से कनेक्ट करें

- इस बिंदु पर डिज़ाइन विंडो के शीर्ष पर हरे रंग की पट्टी से "रन कनेक्शन ऑटोमेशन" पर क्लिक करें। एक बार में एक ब्लॉक के लिए ऐसा करना और ऊपर TX ब्लॉक डिज़ाइन छवि का पालन करना एक अच्छा विचार है।

- उपकरण AXI इंटरकनेक्ट को जोड़ने का प्रयास करेगा, जो AXI-Lite बस (VDMA और GPIO) का उपयोग करने वाले ब्लॉकों के लिए मास्टर/स्लेव इंटरकनेक्ट के रूप में कार्य करता है।

- यह AXI स्मार्टकनेक्ट को भी जोड़ेगा, जो VDMA (स्ट्रीम टू मेमोरी मैप और इसके विपरीत) द्वारा उपयोग किए जाने वाले AXI4-स्ट्रीम और उच्च प्रदर्शन प्रोसेसर इंटरफेस के लिए मास्टर / स्लेव इंटरकनेक्ट के रूप में कार्य करता है।

- उपकरण एक प्रोसेसर सिस्टम रीसेट भी जोड़ देगा। सुनिश्चित करें कि यह केवल वीडीएमए, जीपीआईओ और प्रोसेसर से संबंधित ब्लॉक से जुड़ा है। इसे किसी भी वीडियो ब्लॉक (यानी dvi2rgb, टाइमिंग कंट्रोलर, vid से स्ट्रीम आदि) से कनेक्ट न करें।

- एक बार कनेक्शन स्वचालन पूरा हो जाने के बाद, सत्यापित करें कि कनेक्शन TX ब्लॉक डिज़ाइन छवि से मेल खाते हैं। आप एक अतिरिक्त सिस्टम ILA ब्लॉक देखेंगे जिसका उल्लेख नहीं किया गया है। यह केवल डिबगिंग के लिए है और अभी इसकी आवश्यकता नहीं है। यह 150M प्रोसेसर रीसेट का उपयोग करता है, इसलिए इसकी भी आवश्यकता नहीं है। कहीं भी आपको बसों में छोटे हरे "बग" दिखाई देते हैं, जो कि ILA के कारण होता है और इसे अनदेखा किया जा सकता है।

- अंतिम चरण प्रोजेक्ट सोर्स ट्री में ब्लॉक डिज़ाइन पर राइट क्लिक करना है और "क्रिएट एचडीएल रैपर" का चयन करना है। यदि आप रैपर में तर्क जोड़ने की योजना बना रहे हैं, तो इसे हर बार चुने जाने पर अधिलेखित कर दिया जाएगा।

- एसडीके पक्ष पर विवरण के लिए वीडीएमए चालक सेटअप अनुभाग देखें।

घड़ियां और रीसेट

मैंने पाया है कि किसी भी प्रोग्राम करने योग्य तर्क परियोजना का सबसे महत्वपूर्ण पहलू घड़ी डोमेन और रीसेट सिग्नल पर सावधानीपूर्वक विचार करना है। यदि वे ठीक से कॉन्फ़िगर किए गए हैं तो आपके पास अपना डिज़ाइन काम करने के लिए एक अच्छा शॉट है।

पिक्सेल क्लॉक और टाइमिंग लॉक

यह सत्यापित करने के लिए कि कुछ संकेत सक्रिय हैं, इन संकेतों को एल ई डी (घड़ियों, रीसेट, लॉक आदि) से जोड़ना एक अच्छा विचार है। दो सिग्नल जो मुझे ट्रांसमीटर बोर्ड पर ट्रैक करने में मददगार लगे, वे थे पिक्सेल क्लॉक और AXI4-स्ट्रीम पर वीडियो आउट ब्लॉक पर "लॉक" सिग्नल, जो आपको बताता है कि वीडियो टाइमिंग को टाइमिंग कंट्रोलर और वीडियो स्रोत के साथ सिंक्रोनाइज़ किया गया है। आंकड़े। मैंने डिज़ाइन ब्लॉक रैपर में कुछ तर्क जोड़े हैं जो पिक्सेल घड़ी को रीसेट के रूप में dvi2rgb ब्लॉक पर PixelClkLocked सिग्नल का उपयोग करके ट्रैक करता है। मैंने फ़ाइल को hdmi_wrapper.v के रूप में यहाँ संलग्न किया है। बाधा फ़ाइल भी यहाँ संलग्न है।

चरण 2: रिसीवर के लिए Zynq प्रोग्रामेबल लॉजिक को कॉन्फ़िगर करें

रिसीवर के लिए प्रोग्रामेबल लॉजिक ब्लॉक सरल है। मुख्य अंतर, लापता एचडीएमआई इनपुट ब्लॉक के अलावा, एक पुनर्प्राप्त पिक्सेल घड़ी की अनुपस्थिति है। उस कारण से हमें क्लॉक विजार्ड से अपना जनरेट करना होगा। यह डिजाइन ट्रांसमीटर से अलग प्रोजेक्ट में किया जाना चाहिए। हमारे उद्देश्यों के लिए रिसीवर प्रोजेक्ट ने Zybo 7Z-20 बोर्ड का अनुसरण किया जबकि ट्रांसमीटर ने Z7-10 बोर्ड का अनुसरण किया। बोर्डों पर FPGAs अलग हैं इसलिए…सावधान रहें।

यहाँ रिसीवर डिज़ाइन ब्लॉक बनाने के चरण दिए गए हैं:

-

अपने डिजाइन में निम्नलिखित आईपी ब्लॉक जोड़ें:

- समय नियंत्रक

- AXI4-स्ट्रीम से वीडियो आउट

- आरजीबी से डीवीआई

- एक्सी वीडीएमए

- AXI GPIO

- प्रसंस्करण प्रणाली

- घड़ी जादूगर

- स्थिरांक (VDD 1 पर सेट)

- इन ब्लॉकों को ट्रांसमीटर के रूप में कॉन्फ़िगर करने के लिए उसी पैटर्न का पालन करें। विन्यास में उल्लेखनीय अंतर के लिए छवियां यहां शामिल की गई हैं। अन्य ट्रांसमीटर के समान ही रहते हैं।

- इस डिज़ाइन के लिए VDMA को केवल पठन चैनल के रूप में कॉन्फ़िगर करें। लेखन चैनल अक्षम करें।

-

क्लॉक विजार्ड को निम्न आउटपुट के लिए विन्यस्त किया जाना चाहिए:

- clk_out1: 75 मेगाहर्ट्ज (पिक्सेल घड़ी)

- clk_out2: 150 मेगाहर्ट्ज (स्ट्रीम घड़ी)

- clk_out3: 50 मेगाहर्ट्ज (अक्ष-लाइट घड़ी)

- वीडियो ब्लॉक को कनेक्ट करें जैसा कि आरएक्स ब्लॉक डिजाइन छवि में दिखाया गया है।

- फिर कनेक्शन ऑटोमेशन चलाएँ, जो AXI इंटरकनेक्ट, AXI स्मार्टकनेक्ट और सिस्टम रीसेट ब्लॉक को जोड़ देगा और उपयुक्त कनेक्शन बनाने का प्रयास करेगा। यह सुनिश्चित करने के लिए धीरे-धीरे यहां जाएं कि यह अवांछित कनेक्शन नहीं करता है।

- rgb2dvi ब्लॉक पर HDMI TMDS घड़ी और डेटा पिन बाहरी बनाएं

- इस डिज़ाइन पर हॉट प्लग सिग्नल की कोई आवश्यकता नहीं है।

चरण 3: सेटअप VDMA ड्राइवर

AXI-Lite इंटरफ़ेस के माध्यम से कॉन्फ़िगर किए गए विभिन्न ब्लॉकों के लिए सेटअप को संदर्भ के रूप में BSP के साथ शामिल डेमो प्रोजेक्ट्स का उपयोग करके सबसे अच्छा किया जाता है। डिज़ाइन हार्डवेयर निर्यात करने और विवाडो से एसडीके लॉन्च करने के बाद, आप एक नया बोर्ड समर्थन पैकेज जोड़ना चाहेंगे और बीएसपी सेटिंग्स विंडो पर lwip202 लाइब्रेरी शामिल करना चाहेंगे। बसपा से system.mss फ़ाइल फ़ाइल खोलें और आप अपने ब्लॉक डिज़ाइन से मौजूद परिधीय ड्राइवर देखेंगे। "आयात उदाहरण" विकल्प आपको डेमो प्रोजेक्ट आयात करने देता है जो इन बाह्य उपकरणों का उपयोग करते हैं और इस प्रकार आपको दिखाते हैं कि उपलब्ध Xilinx ड्राइवरों का उपयोग करके सॉफ़्टवेयर में उन्हें कैसे कॉन्फ़िगर किया जाए (संलग्न छवि देखें)।

यह वीडीएमए, टाइमर और इंटरप्ट, और जीपीआईओ को कॉन्फ़िगर करने के लिए उपयोग की जाने वाली विधि थी। ट्रांसमिट और रिसीव दोनों के सोर्स कोड को यहां शामिल किया गया है। मतभेद लगभग अनन्य रूप से main.c.

***नोट: चूंकि इस ट्यूटोरियल को लिखने के समय सिस्टम पूरी तरह कार्यात्मक नहीं है, इसलिए इस खंड के स्रोत कोड में वायरलेस नेटवर्क कोड शामिल नहीं है। नेटवर्क ट्रांसमिट/प्राप्त परियोजनाओं के साथ वीडियो कोर ट्रांसमिट/प्राप्त परियोजनाओं के संयोजन के परिणामस्वरूप कई बगों को संबोधित करने की आवश्यकता है। इसलिए यह ट्यूटोरियल कुछ समय के लिए उनके साथ अलग व्यवहार करता है।***

TX इंटरप्ट हैंडलर फंक्शन (IRQHandler)

यह फ़ंक्शन GPIO ब्लॉक के माध्यम से VDMA को पढ़ने और लिखने दोनों द्वारा प्रदान किए गए ग्रे कोड को पढ़ता है। ग्रे कोड को दशमलव में बदल दिया जाता है और वर्तमान फ्रेम के फ्रेम बेस मेमोरी लोकेशन का चयन करने के लिए उपयोग किया जाता है। कॉपी किया गया फ्रेम वीडीएमए द्वारा लिखे गए पिछले फ्रेम है (उदाहरण के लिए अगर वीडीएमए फ्रेम 2 के लिए लिख रहा है, तो हम फ्रेम 1 की प्रतिलिपि बनाते हैं; अगर फ्रेम 0 पर लिखते हैं, तो हम फ्रेम 2 से लपेटते हैं और पढ़ते हैं)।

फ़ंक्शन केवल 60 हर्ट्ज के बजाय फ्रेम दर को 10 हर्ट्ज तक कम करने के लिए प्रत्येक 6 वें फ्रेम को कैप्चर करता है। नेटवर्क की ऊपरी सीमा 300 एमबीपीएस है। 10 फ्रेम प्रति सेकेंड पर 221.2 एमबीपीएस की बैंडविड्थ की आवश्यकता होती है।

इस फ़ंक्शन में दो पंक्तियों पर टिप्पणी/अन-टिप्पणी करना उपयोगकर्ता को डिबगिंग/परीक्षण उद्देश्यों के लिए एचडीएमआई पासथ्रू मोड में बदलने की अनुमति देगा (उपयुक्त लाइनों को इंगित करने के लिए कोड पर टिप्पणी की गई है)। यह वर्तमान में फ़्रेम को ईथरनेट कोड द्वारा उपयोग किए जाने वाले मेमोरी लोकेशन पर कॉपी करता है।

RX इंटरप्ट हैंडलर फंक्शन (IRQHandler)

यह फ़ंक्शन TX फ़ंक्शन के समान है, लेकिन यह आने वाले डेटा को लिखने के लिए ईथरनेट द्वारा उपयोग किए जाने वाले 2 बफर FIFO से कॉपी करता है। ईथरनेट कोड इंगित करता है कि कौन सा फ्रेम फीफो को लिखा जा रहा है, डेटा विपरीत फ्रेम से कॉपी किया गया है। डेटा को वीडीएमए द्वारा पढ़े जा रहे फ्रेम के ठीक पीछे फ्रेम में कॉपी किया जाता है ताकि फटने से बचा जा सके।

चरण 4: सेटअप नैनोराउटर नेटवर्क

टीपीलिंक नैनोराउटर का उपयोग करके नेटवर्क बनाने के लिए, उन्हें अलग-अलग चालू करें और उपकरणों के लिए डिफ़ॉल्ट वाईफाई एसएसआईडी से कनेक्ट करें। इस विशेष डिवाइस के लिए कॉन्फ़िगरेशन सेटिंग्स के बारे में अधिक जानकारी डिवाइस उपयोगकर्ता मैनुअल के माध्यम से मिल सकती है।

उपकरणों में से एक को एक्सेस प्वाइंट के रूप में सेटअप करें, यह नेटवर्क के लिए प्राथमिक कनेक्शन के रूप में कार्य करेगा। नेटवर्क को नाम देना और नाम नोट करना सुनिश्चित करें, और डीएचसीपी को अक्षम करें (हम नहीं चाहते कि राउटर आईपी एड्रेस को गतिशील रूप से कॉन्फ़िगर करे, हम चाहते हैं कि टैन्समीटर और रिसीवर ज़ीबो बोर्ड अपने आईपी पते स्वयं सेट करें ताकि वे सुसंगत हों)। कॉन्फ़िगर करने के बाद, सुनिश्चित करें कि डिवाइस रीबूट होता है और इस नेटवर्क को स्थापित करता है।

अन्य डिवाइस को क्लाइंट के रूप में सेटअप करें, और सुनिश्चित करें कि यह नेटवर्क SSID से कनेक्ट होता है जिसे आपने पहले नैनोराउटर के साथ सेटअप किया है। एक बार फिर, सुनिश्चित करें कि क्लाइंट के लिए DHCP अक्षम है।

एक बार जब क्लाइंट समाप्त हो जाता है और रीबूट हो जाता है, तो उसे एक्सेस प्वाइंट नैनोराउटर से कनेक्ट होना चाहिए (यदि ऐसा नहीं होता है, तो डिवाइस में से किसी एक के आपके कॉन्फ़िगरेशन में कोई समस्या हो सकती है)। आप देखेंगे कि एक्सेस प्वाइंट से कनेक्ट होने के बाद क्लाइंट पर एलईडी लाइट ठोस हो जाएगी।

एक्सेस प्वाइंट नैनोराउटर एलईडी इस बिंदु पर चमकती रहेगी, यह ठीक है! चमकती रोशनी का मतलब है कि यह अपने ईथरनेट पोर्ट से किसी अन्य डिवाइस से कनेक्ट नहीं है, और एक बार कॉन्फ़िगर किए गए ज़ीबो से कनेक्ट होने के बाद एलईडी एक सफल नेटवर्क कनेक्शन का संकेत देने वाला ठोस रहेगा।

अब जब हमारे पास हमारे नैनोराउटर सेटअप हैं, तो हमारे पास एक वायरलेस नेटवर्क है जो हमें संचार करने की अनुमति देगा। एक महत्वपूर्ण नोट यह है कि नैनोराउटर (एक्सेस पॉइंट और क्लाइंट के रूप में) के लिए हमारी कॉन्फ़िगरेशन विधि हमें ट्रांसमिटिंग ज़ीबो बोर्ड से प्राप्त करने वाले ज़ीबो बोर्ड तक संचार करने की अनुमति देती है जैसे कि दोनों एक ही ईथरनेट तार से जुड़े थे। यह हमारे नेटवर्क सेटअप को कम कठिन बनाता है, क्योंकि विकल्प में संभावित रूप से इच्छित कनेक्शन के साथ स्पष्ट रूप से सर्वर से कनेक्ट करने के लिए Zybo बोर्डों को कॉन्फ़िगर करना शामिल होगा।

एक बार दोनों डिवाइस सेटअप हो जाने के बाद, नैनोराउटर कॉन्फ़िगर हो जाते हैं और आपके WIDI नेटवर्क में लागू होने के लिए तैयार हो जाते हैं। नैनोराउटर और ज़ीबो बोर्ड के बीच कोई विशिष्ट जोड़ी नहीं है, क्योंकि या तो एक्सेस प्वाइंट या क्लाइंट ट्रांसमिट या रिसीव डिवाइस के लिए काम करेगा।

चरण 5: ईथरनेट के माध्यम से डेटा ट्रांसमिशन के लिए Zynq प्रोसेसिंग सिस्टम सेटअप करें

एचडीएमआई डेटा को एक ज़ीबो बोर्ड से दूसरे में प्रसारित करने के लिए, हमें अपने वीडीएमए ड्राइवर के साथ एक ईथरनेट प्रोटोकॉल शामिल करना होगा। यहां हमारा लक्ष्य प्रोसेसिंग सिस्टम में ईथरनेट पेरिफेरल के माध्यम से अलग-अलग वीडियो फ्रेम को एक निर्धारित दर पर स्ट्रीम करना है जो हमारे नेटवर्क बैंडविड्थ के अनुरूप है। हमारे प्रोजेक्ट के लिए, हमने बेयर-मेटल LwIP API द्वारा प्रदान किए गए TCP का उपयोग किया। चूंकि परियोजना के दोनों सदस्य नेटवर्किंग उपयोगिताओं के साथ अपेक्षाकृत अनुभवहीन हैं, इसलिए यह चुनाव टीसीपी से जुड़े निहितार्थों और बाधाओं को पूरी तरह से पहचाने बिना किया गया था। इस कार्यान्वयन के साथ प्रमुख समस्या सीमित बैंडविड्थ थी और तथ्य यह है कि यह वास्तव में डेटा की उच्च मात्रा को भाप देने के उद्देश्य से नहीं बनाया गया है। इस परियोजना में टीसीपी को बदलने और सुधार करने के वैकल्पिक समाधानों पर बाद में चर्चा की जाएगी।

LwIP के साथ TCP का संक्षिप्त विवरण: डेटा को नेटवर्क पर tcp_mss (TCP अधिकतम खंड आकार) के पैकेट में भेजा जाता है, जो आमतौर पर 1460 बाइट्स होता है। tcp_write को कॉल करने से पॉइंटर द्वारा संदर्भित कुछ डेटा लिया जाएगा और डेटा को होल्ड करने और TCP संचालन के लिए एक संरचना प्रदान करने के लिए pbufs (पैकेट बफ़र्स) को कॉन्फ़िगर किया जाएगा। एक बार में कतारबद्ध किए जा सकने वाले डेटा की अधिकतम मात्रा को tcp_snd_buf (TCP प्रेषक बफ़र स्थान) के रूप में सेट किया जाता है। चूंकि यह पैरामीटर एक 16 बिट संख्या है, हम 59695 बाइट्स के भेजने वाले बफर आकार तक सीमित हैं (भेजें बफर में कुछ आवश्यक पैडिंग है)। एक बार डेटा कतारबद्ध हो जाने के बाद, डेटा संचारित करना शुरू करने के लिए tcp_output को कॉल किया जाता है। डेटा के अगले खंड को भेजने से पहले, यह जरूरी है कि पिछले सभी पैकेट सफलतापूर्वक प्रसारित हो गए हों। यह प्रक्रिया recv_callback फ़ंक्शन का उपयोग करके की जाती है, क्योंकि यह वह फ़ंक्शन है जिसे तब कहा जाता है जब रिसीवर से पावती देखी जाती है।

विवाडो एसडीके में उदाहरण परियोजनाओं का उपयोग करना सीखने के लिए बहुत मददगार है कि एलडब्ल्यूआईपी टीसीपी ऑपरेशन कैसे होता है, और एक नई परियोजना शुरू करने के लिए एक अच्छा प्रारंभिक बिंदु है।

वाईडीआई ट्रांसमिटिंग डिवाइस की प्रक्रिया इस प्रकार है:

- बेयर-मेटल LWIP ड्राइवर फ़ंक्शन कॉल का उपयोग करके TCP नेटवर्क को प्रारंभ करें।

- नेटवर्क संचालन के लिए आवश्यक कोई भी कॉलबैक फ़ंक्शन निर्दिष्ट करें।

- इसके आईपी पते और पोर्ट से कनेक्ट करके वाईडीआई रिसीवर से कनेक्ट करें (हमारा कॉन्फ़िगरेशन: रिसीवर आईपी 192.168.0.9 है, पोर्ट 7 से कनेक्ट करें)।

- जब VDMA ड्राइवर टाइमर समाप्त हो जाता है, तो TX ISR दर्ज करें।

- वीडीएमए ग्रे कोड के आधार पर एक्सेस करने के लिए वर्तमान फ्रेम बफर निर्धारित करें

- टीसीपी भेजने वाले बफर में डेटा के पहले खंड को कतारबद्ध करें

- डेटा को आउटपुट करें, और वर्तमान फ्रेम से कितना डेटा भेजा गया है, इसका ट्रैक रखने के लिए स्थानीय चर अपडेट करें।

- प्राप्त कॉलबैक तक पहुंचने पर (ट्रांसमीटर को डेटा पुनर्प्राप्ति की पावती मिलने के बाद किया गया फ़ंक्शन कॉल), डेटा के अगले खंड को कतारबद्ध करें।

- चरण 7 और 8 को तब तक दोहराएं जब तक कि पूरा फ्रेम नहीं भेजा जाता।

- एक नया फ्रेम तैयार है यह इंगित करने के लिए अगले टाइमर बाधा की प्रतीक्षा करने के लिए एक निष्क्रिय स्थिति पर लौटें (चरण 4 पर वापस जाएं)।

जैसा कि ऊपर की छवि में दिखाया गया है, बोर्ड सपोर्ट पैकेज LwIP सेटिंग्स को सेटअप करना सुनिश्चित करें। tcp_snd_buf, tcp_pueue_ooseq, mem_size, memp_n_tcp_seg को छोड़कर सभी मान डिफ़ॉल्ट हैं। यह भी ध्यान दें कि डिबग_ऑप्शन समूह के लिए बीएसपी मापदंडों को बदलकर विस्तृत डिबगिंग प्राप्त की जा सकती है।

चरण 6: ईथरनेट के माध्यम से डेटा रिसेप्शन के लिए Zynq प्रोसेसिंग सिस्टम सेटअप करें

Zybo डेवलपमेंट बोर्ड जो वायरलेस रिसीवर के रूप में कार्य करेगा, ट्रांसमिटिंग डिवाइस के समान ही काम करेगा। एलडब्ल्यूआईपी के लिए बोर्ड समर्थन पैकेज सेटिंग्स पिछले चरण के समान होंगी।

डिवाइस नैनोराउटर से वीडियो फ्रेम सेगमेंट वाले पैकेट में ले जाएगा, और यह वीडीएमए प्राप्त करने के लिए वीडियो फ्रेम डेटा को ट्रिपल फ्रेम बफर स्पेस में कॉपी करेगा। किसी भी डेटा को ओवरराइट करने से बचने के लिए, एक डबल डेटा बफर (जिसे हम नेटवर्क बफर के रूप में संदर्भित करेंगे) का उपयोग नैनोराउटर से डेटा एकत्र करते समय किया जाता है, ताकि नेटवर्क ट्रैफ़िक स्ट्रीमिंग जारी रख सके, जबकि पिछले पूर्ण वीडियो फ़्रेम की प्रतिलिपि बनाई जा रही है। वीडीएमए बफर।

वाईडीआई प्राप्त करने वाले डिवाइस की प्रक्रिया के लिए दो कार्यों की आवश्यकता होती है, जिनमें से एक ईथरनेट डेटा प्राप्त कर रहा है, और दूसरा नेटवर्क बफर से वीडीएमए के ट्रिपल फ्रेम बफर में वीडियो फ्रेम की प्रतिलिपि बना रहा है।

ईथरनेट रिसेप्शन कार्य:

- बेयर-मेटल LWIP ड्राइवर फ़ंक्शन कॉल का उपयोग करके TCP नेटवर्क को प्रारंभ करें (आईपी पते के साथ सेटअप जो ट्रांसमीटर से कनेक्ट होगा, हमारे में 192.168.0.9)

- नेटवर्क संचालन के लिए आवश्यक कोई भी कॉलबैक फ़ंक्शन निर्दिष्ट करें।

- ईथरनेट पैकेट प्राप्त होने पर, पैकेट डेटा को वर्तमान नेटवर्क बफर में कॉपी करें, वर्तमान संचित डेटा को बढ़ाएं।

- यदि पैकेट नेटवर्क फ्रेम बफर भरता है, तो चरण 5 और 6 पर जारी रखें। अन्यथा, इस कार्य के लिए चरण 3 पर वापस लूप करें।

- संकेत है कि वीडीएमए ट्रिपल फ्रेम बफर कार्य को नए समाप्त नेटवर्क बफर से कॉपी करना चाहिए।

- अन्य नेटवर्क बफर पर स्विच करें और ईथरनेट के माध्यम से डेटा एकत्र करना जारी रखें।

- नया ईथरनेट पैकेट प्राप्त होने तक निष्क्रिय (चरण 3)।

नेटवर्क बफर को VDMA ट्रिपल फ्रेम बफर में कॉपी करें:

- जब VDMA ड्राइवर टाइमर समाप्त हो जाए, तो RX ISR दर्ज करें।

- वीडीएमए ग्रे कोड के आधार पर एक्सेस करने के लिए वर्तमान फ्रेम बफर निर्धारित करें।

- निर्धारित करें कि कौन सा नेटवर्क बफ़र VDMA बफ़र में कॉपी किया जाएगा, और उस डेटा को कॉपी करें

चरण 7: अपने Zybo बोर्डों को HDMI स्रोत और HDMI सिंक से कनेक्ट करें

अब रिसीवर और ट्रांसमीटर दोनों के लिए एचडीएमआई केबल कनेक्ट करें, एफपीजीए प्रोग्राम करें और प्रोसेसिंग सिस्टम चलाएं। एलडब्ल्यूआईपी संचालन और सीमित बैंडविड्थ में अत्यधिक ओवरहेड के कारण फ्रेम दर बहुत धीमी होगी। यदि कोई समस्या है, तो UART के माध्यम से जुड़ें और किसी भी चेतावनी या त्रुटियों की पहचान करने का प्रयास करें।

चरण 8: सुधार के लिए वैकल्पिक विचार

इस परियोजना के लिए एक बड़ा मुद्दा वाईफाई पर भेजने के लिए आवश्यक डेटा की मात्रा थी। यह अपेक्षित था, हालांकि हमने इसके प्रभाव को कम करके आंका और इसके परिणामस्वरूप वीडियो फ़ीड के बजाय स्क्रीन पर छवियों का अधिक विस्फोट हुआ। इस परियोजना को बेहतर बनाने के कई तरीके हैं:

- वास्तविक समय वीडियो संपीड़न। आने वाले वीडियो फ़ीड फ़्रेम को फ़्रेम द्वारा संपीड़ित करने से नेटवर्क पर भेजने के लिए आवश्यक डेटा की मात्रा बहुत कम हो जाएगी। आदर्श रूप से यह हार्डवेयर में किया जाएगा (जो एक आसान काम नहीं है), या यह एक संपीड़न एल्गोरिदम चलाने के लिए अन्य एआरएम कोर का उपयोग करके सॉफ्टवेयर में किया जा सकता है (यह सुनिश्चित करने के लिए कुछ और विश्लेषण की आवश्यकता होगी कि समय काम करता है)। कुछ ओपन सोर्स रियल टाइम वीडियो कम्प्रेशन घटक हैं जो हमें वेब पर मिले हैं, लेकिन अधिकांश आईपी हैं।

- सॉफ्टवेयर के बजाय हार्डवेयर में ईथरनेट स्ट्रीम को लागू करना। सेगमेंट आकार पर सीमा के कारण ट्रांसमीटर में आउटगोइंग डेटा को कतार में उपलब्ध स्थान की कमी के कारण ओवरहेड का एक टन था। इसमें डेटा फीड करने के लिए FIFO बफर या DMA के साथ AXI इथरनेट IP का उपयोग करना एक अधिक कुशल प्रक्रिया है। यह एलडब्ल्यूआईपी टीसीपी से अतिरिक्त सामान को कम करेगा और अधिक डेटा प्रवाह की अनुमति देगा।

चरण 9: अभिगम्यता

इस वाईडीआई परियोजना का परिणामी उत्पाद उपकरणों की एक पूरी तरह से एकीकृत, कॉम्पैक्ट जोड़ी होनी चाहिए जिसे उपयोगकर्ता किसी भी एचडीएमआई स्रोत से कनेक्ट कर सकता है और फिर वीडियो फ़ीड को एचडीएमआई क्षमता वाले डिस्प्ले में वायरलेस तरीके से सिंक कर सकता है। उपकरणों में Zynq-7000 SoC होगा जो Zybo संदर्भ बोर्ड पर पाया जाएगा और TP-Link नैनो-राउटर में पाए जाने वाले नेटवर्क हार्डवेयर को शामिल करेगा। आदर्श रूप से, उपयोगकर्ता महत्वपूर्ण तकनीकी क्षमता की बहुत कम आवश्यकता के साथ, लक्ष्य ऑपरेटिंग सिस्टम के भीतर एक असतत स्थान से ट्रांसमिट मॉड्यूल को नियंत्रित करने में सक्षम होगा।

सुरक्षा और कनेक्टिविटी

उपकरणों में ट्रांसपोर्ट लेयर सिक्योरिटी (TLS) भी शामिल होनी चाहिए और गोपनीयता उद्देश्यों के लिए दोनों में सीमित ऑटो-कनेक्ट क्षमता होनी चाहिए। यह डिजाइनरों का इरादा है कि वायरलेस इंटरफेस पर डिस्प्ले के साथ कनेक्शन को उपयोगकर्ता की ओर से एक जानबूझकर कार्रवाई करने के लिए गलती से संवेदनशील सामग्री प्रसारित करने से बचने के लिए।

वर्तमान स्थिति

इस बिंदु तक, परियोजना की स्थिति अभी भी बहुत काम प्रगति पर है। वर्तमान एंड-पॉइंट उपयोगकर्ता के लिए इस ट्यूटोरियल से लाभान्वित होने के लिए, उसे एम्बेडेड सिस्टम डिज़ाइन की एक मजबूत तकनीकी समझ होनी चाहिए और प्रोग्राम योग्य हार्डवेयर और एम्बेडेड सॉफ़्टवेयर के साथ मिलकर काम करने के साथ कुछ परिचित होना चाहिए।

नेटवर्क पर भेजा जा रहा डेटा इस बिंदु पर एन्क्रिप्टेड नहीं है और इसे टीसीपी/आईपी पैकेट का कच्चा प्रसारण माना जाता है।

वीडियो कोर प्रोजेक्ट को ट्रांसमिट और रिसीव दोनों के लिए सफलतापूर्वक परीक्षण किया गया था। दूसरी ओर, दो zybo बोर्डों के बीच वायरलेस कनेक्शन स्थापित किया गया था और परीक्षण फ़्रेम डेटा सफलतापूर्वक भेजा गया था। हालाँकि, यह अभी भी आवश्यक है कि नेटवर्क कोड को प्रत्येक वीडियो कोर प्रोजेक्ट में संयोजित किया जाए और वास्तविक वीडियो फ़्रेम के प्रसारण का परीक्षण किया जाए।

सिफारिश की:

M5stack Esp32 आधारित M5stick C डेवलपमेंट बोर्ड के साथ Flappy बर्ड गेम खेलना: 5 कदम

M5stack Esp32 आधारित M5stick C डेवलपमेंट बोर्ड के साथ Flappy Bird गेम खेलना: हाय दोस्तों आज हम सीखेंगे कि कैसे m5stack द्वारा प्रदान किए गए m5stick c डेवलपमेंट बोर्ड पर फ़्लैपी बर्ड गेम कोड अपलोड करें। इस छोटे प्रोजेक्ट के लिए आपको निम्नलिखित दो चीजों की आवश्यकता होगी: m5stick-c विकास बोर्ड: https://www.utsource.net/itm/p/8663561.h

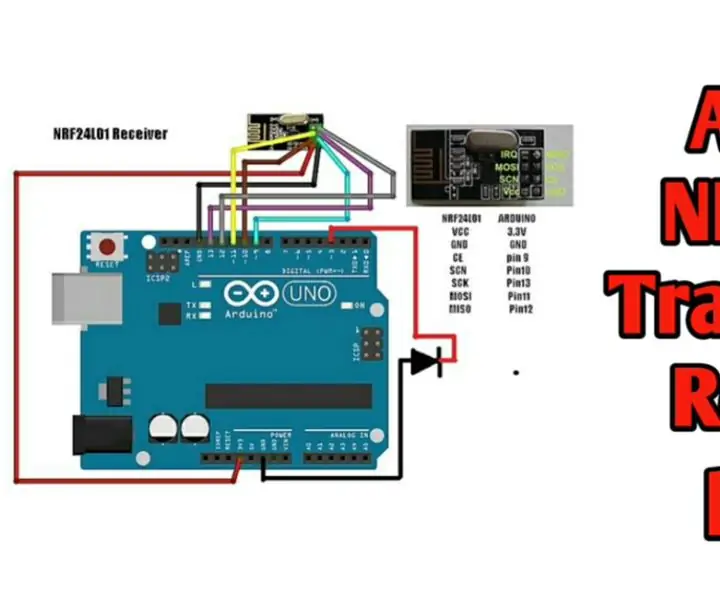

Arduino के साथ 2.4Ghz NRF24L01 मॉड्यूल का उपयोग कर वायरलेस रिमोट - क्वाडकॉप्टर के लिए Nrf24l01 4 चैनल / 6 चैनल ट्रांसमीटर रिसीवर - आरसी हेलीकाप्टर - Arduino का उपयोग करते हुए Rc प्लेन: 5 कदम (चित्रों के साथ)

Arduino के साथ 2.4Ghz NRF24L01 मॉड्यूल का उपयोग कर वायरलेस रिमोट | क्वाडकॉप्टर के लिए Nrf24l01 4 चैनल / 6 चैनल ट्रांसमीटर रिसीवर | आरसी हेलीकाप्टर | Arduino का उपयोग करते हुए Rc प्लेन: Rc कार चलाने के लिए | क्वाडकॉप्टर | ड्रोन | आरसी विमान | RC नाव, हमें हमेशा एक रिसीवर और ट्रांसमीटर की आवश्यकता होती है, मान लीजिए कि RC QUADCOPTER के लिए हमें एक 6 चैनल ट्रांसमीटर और रिसीवर की आवश्यकता है और उस प्रकार का TX और RX बहुत महंगा है, इसलिए हम अपने

JALPIC वन डेवलपमेंट बोर्ड: 5 कदम (चित्रों के साथ)

JALPIC वन डेवलपमेंट बोर्ड: यदि आप मेरे इंस्ट्रक्शंस प्रोजेक्ट्स का पालन करते हैं, तो आप जानते हैं कि मैं PIC माइक्रोकंट्रोलर के संयोजन में JAL प्रोग्रामिंग भाषा का बहुत बड़ा प्रशंसक हूं। JAL एक पास्कल जैसी प्रोग्रामिंग भाषा है जिसे माइक्रोचिप के 8-बिट PIC माइक्रोकंट्रोलर के लिए विकसित किया गया है। मो

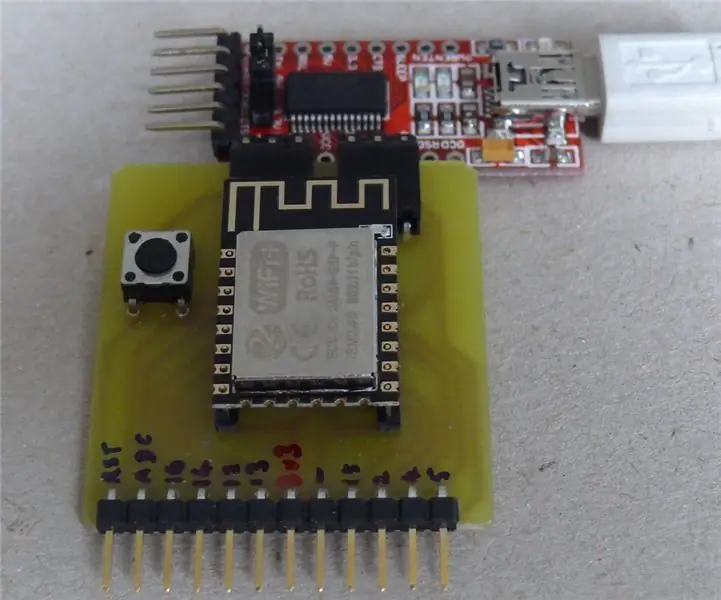

ESP-12E और ESP-12F प्रोग्रामिंग एंड डेवलपमेंट बोर्ड: 3 चरण (चित्रों के साथ)

ESP-12E और ESP-12F प्रोग्रामिंग और विकास बोर्ड: इस बोर्ड के लिए प्रेषण सरल था: ESP-12E और ESP-12F मॉड्यूल को NodeMCU बोर्डों की तरह आसानी से प्रोग्राम करने में सक्षम हो (यानी बटन दबाने की कोई आवश्यकता नहीं)। प्रयोग करने योग्य IO तक पहुंच के साथ ब्रेडबोर्ड के अनुकूल पिन रखें। सीरियल कनवे के लिए एक अलग USB का उपयोग करें

ऑरेंज पीआई कैसे करें: इसे 5" एचडीएमआई टीएफटी एलसीडी डिस्प्ले के साथ उपयोग करने के लिए सेट करें: 8 कदम (चित्रों के साथ)

ऑरेंज पीआई कैसे करें: इसे 5 "एचडीएमआई टीएफटी एलसीडी डिस्प्ले के साथ उपयोग करने के लिए सेट करें: यदि आप अपने ऑरेंज पीआई के साथ एक एचडीएमआई टीएफटी एलसीडी डिस्प्ले ऑर्डर करने के लिए पर्याप्त समझदार थे, तो आप शायद इसे काम करने के लिए मजबूर करने की कोशिश में कठिनाइयों से निराश हैं जबकि अन्य किसी बाधा को नोट भी नहीं कर पाए। मुख्य बात यह है कि कुछ