विषयसूची:

- चरण 1: वीएचडीएल और मॉडलिम

- चरण 2: डिजाइन और परीक्षण पीठ के लिए वीएचडीएल कोड

- चरण 3: फ़ाइलें संलग्न

- चरण 4: मिनी-कॉर्डिक आईपी कोर - 16 बिट

वीडियो: वीएचडीएल का उपयोग कर कॉर्डिक एल्गोरिथम: 4 कदम

2024 लेखक: John Day | [email protected]. अंतिम बार संशोधित: 2024-01-30 09:19

AmCoderhttps://www.linkedin.com/in/mitu द्वारा लेखक द्वारा अधिक अनुसरण करें:

के बारे में: मितु राज - जस्ट ए हॉबीस्ट एंड लर्नर - चिप डिज़ाइनर - सॉफ्टवेयर डेवलपर - भौतिकी और गणित उत्साही एमकोडर के बारे में अधिक »

##साइन और कोसाइन तरंग उत्पन्न करने के लिए कॉर्डिक एल्गोरिथम के वीएचडीएल कार्यान्वयन के लिए यह Google में सबसे अधिक क्लिक की जाने वाली, लोकप्रिय लिंक है## वर्तमान समय में, कई हार्डवेयर कुशल एल्गोरिदम मौजूद हैं, लेकिन सॉफ्टवेयर सिस्टम के प्रभुत्व के कारण ये अच्छी तरह से ज्ञात नहीं हैं कई साल। कॉर्डिक एक ऐसा एल्गोरिथम है जो कुछ भी नहीं बल्कि शिफ्ट का एक सेट है और कुछ त्रिकोणमितीय, अतिशयोक्तिपूर्ण, रैखिक और लॉगरिदमिक कार्यों सहित कार्यों की एक विस्तृत श्रृंखला की गणना के लिए उपयोग किए जाने वाले तर्क जोड़ें। यह कैलकुलेटर आदि में उपयोग किया जाने वाला एल्गोरिथम है। इस प्रकार केवल साधारण शिफ्टर्स और एडर्स का उपयोग करके हम कॉर्डिक एल्गोरिथम का उपयोग करके कम जटिलता लेकिन डीएसपी की शक्ति के साथ एक हार्डवेयर डिजाइन कर सकते हैं। इसलिए इसे बिना किसी समर्पित फ्लोटिंग पॉइंट यूनिट या जटिल गणित आईपी का उपयोग किए बिना वीएचडीएल या वेरिलोग में नंगे आरटीएल डिजाइन के रूप में डिजाइन किया जा सकता है।

चरण 1: वीएचडीएल और मॉडलिम

यहां कॉर्डिक एल्गोरिथम को साइन वेव और कोस वेव उत्पन्न करने के लिए वीएचडीएल का उपयोग करके लागू किया गया है। यह बड़ी सटीकता पर इनपुट कोण के साइन और कोसाइन का उत्पादन कर सकता है। कोड FPGA पर संश्लेषित किया जा सकता है। मॉडलिम का उपयोग डिजाइन और परीक्षण बेंच का अनुकरण करने के लिए किया जाता है।

चरण 2: डिजाइन और परीक्षण पीठ के लिए वीएचडीएल कोड

बाइनरी स्केलिंग तकनीक का उपयोग फ्लोटिंग पॉइंट नंबरों को दर्शाने के लिए किया जाता है।

कृपया कोड करने से पहले संलग्न डॉक्स को देखें।

कॉर्डिक_v4.vhd - डिज़ाइन -इनपुट 32 बिट्स + साइन बिट में एंगल है; यह ०.००००००००२३३ डिग्री के इनपुट परिशुद्धता के साथ ० से +/-३६० डिग्री तक किसी भी कोण को संसाधित कर सकता है। इनपुट देते समय -> MSB साइन बिट होता है और बाकी 32 बिट्स परिमाण का प्रतिनिधित्व करते हैं।-डिजाइन का आउटपुट 16 बिट्स + साइन बिट में इसका साइन और कॉस वैल्यू होता है। सटीक 0.00001526 के साथ। कृपया ध्यान दें कि यदि संबंधित साइन या कॉस वैल्यू नकारात्मक है तो आउटपुट 2 के कॉम्प्लिमेंट फॉर्म में प्रदर्शित होता है। सिमुलेटिंग testb.vhd - डिज़ाइन के लिए टेस्ट बेंच (1) इनपुट एंगल और पुल रीसेट = '0'। सिमुलेशन के दो चरणों के बाद '1' पर रीसेट करें और "सभी चलाएं"। (2) सिमुलेशन विंडो में पाप और कॉस सिग्नल के रेडिक्स को दशमलव और प्रारूप> एनालॉग (स्वचालित) के रूप में सेट करें। (3) तरंग देखने के लिए ज़ूम आउट करें अच्छी तरह से।

चरण 3: फ़ाइलें संलग्न

(1) कॉर्डिक_वी4.वीएचडी - डिज़ाइन। (2) टेस्टबी.वीएचडी - डिज़ाइन के लिए टेस्ट बेंच।

(३) कोण इनपुट को बाध्य करने और बाइनरी परिणामों को परिवर्तित करने के तरीके पर दस्तावेज़।

अद्यतन: ये फ़ाइलें अप्रचलित हैं और अब उपलब्ध नहीं हैं। कृपया अगले चरण से फ़ाइलों का उपयोग करें।

चरण 4: मिनी-कॉर्डिक आईपी कोर - 16 बिट

उपरोक्त कार्यान्वयन की सीमा है- एक घड़ी चक्र में गणना करने के कारण धीमी, कम घड़ी की आवृत्ति। मिनी-कॉर्डिक आईपी कोर - 16 बिट

- प्रदर्शन में सुधार के लिए कई चक्रों को वितरित महत्वपूर्ण पथ।- तेज़ - FPGA सिद्ध डिज़ाइन को 100 मेगाहर्ट्ज घड़ी तक संश्लेषित किया गया।- एचडीएल में अनुकूलित अधिक क्षेत्र, कम हार्डवेयर।- लोड और पूर्ण स्थिति सिग्नल जोड़े गए।- केवल नकारात्मक पक्ष की तुलना में कम रिज़ॉल्यूशन है पिछला एक। टेस्टबेंच:

0 से 360 डिग्री कोण इनपुट से पूरी तरह से स्वचालित

संलग्न फ़ाइलें: 1) मिनी कॉर्डिक मुख्य वीएचडीएल फ़ाइल 2) मिनी कॉर्डिक टेस्ट बेंच 3) मिनी कॉर्डिक आईपी कोर मैनुअल 4) कोणों को बल देने और परिणामों को परिवर्तित करने के तरीके पर डॉक्टर

किसी भी प्रश्न के लिए, मुझसे बेझिझक संपर्क करें:

मीतू राजो

मुझे फॉलो करें:

मेल: [email protected]

###कुल डाउनलोड: 01-05-2021 तक 325###

### अंतिम बार संपादित कोड: जुलाई-07-2020 ###

सिफारिश की:

सेल्फ बैलेंसिंग रोबोट - पीआईडी कंट्रोल एल्गोरिथम: 3 कदम

सेल्फ बैलेंसिंग रोबोट - पीआईडी कंट्रोल एल्गोरिथम: इस परियोजना की कल्पना इसलिए की गई थी क्योंकि मुझे कंट्रोल एल्गोरिदम के बारे में अधिक जानने और कार्यात्मक पीआईडी लूप को प्रभावी ढंग से लागू करने के तरीके के बारे में जानने में दिलचस्पी थी। यह परियोजना अभी भी विकास के चरण में है क्योंकि एक ब्लूटूथ मॉड्यूल को जोड़ा जाना बाकी है जो सभी

बोर्ड गेम आर्टिफिशियल इंटेलिजेंस: मिनिमैक्स एल्गोरिथम: 8 कदम

बोर्ड गेम आर्टिफिशियल इंटेलिजेंस: मिनिमैक्स एल्गोरिथम: क्या आपने कभी सोचा है कि शतरंज या चेकर्स में आप जिन कंप्यूटरों के खिलाफ खेलते हैं, वे कैसे बनते हैं? अच्छी तरह से इस निर्देश से आगे नहीं देखें, यह आपको दिखाएगा कि मिनिमैक्स एल्गोरिथम का उपयोग करके एक सरल लेकिन प्रभावी कृत्रिम बुद्धिमत्ता (एआई) कैसे बनाई जाए! वें का उपयोग करके

वीएचडीएल और बेसिस3 बोर्ड का उपयोग कर बुनियादी स्टॉपवॉच: 9 कदम

VHDL और Basys3 बोर्ड का उपयोग करके बेसिक स्टॉपवॉच: बेसिक VHDL और बेसिस 3 बोर्ड का उपयोग करके स्टॉपवॉच कैसे बनाएं, इस निर्देश में आपका स्वागत है। हम आपके साथ अपनी परियोजना साझा करने के लिए उत्साहित हैं! यह पतन २०१६ में कैल पॉली, एसएलओ में पाठ्यक्रम सीपीई १३३ (डिजिटल डिजाइन) के लिए एक अंतिम परियोजना थी। हम जिस परियोजना का निर्माण कर रहे हैं

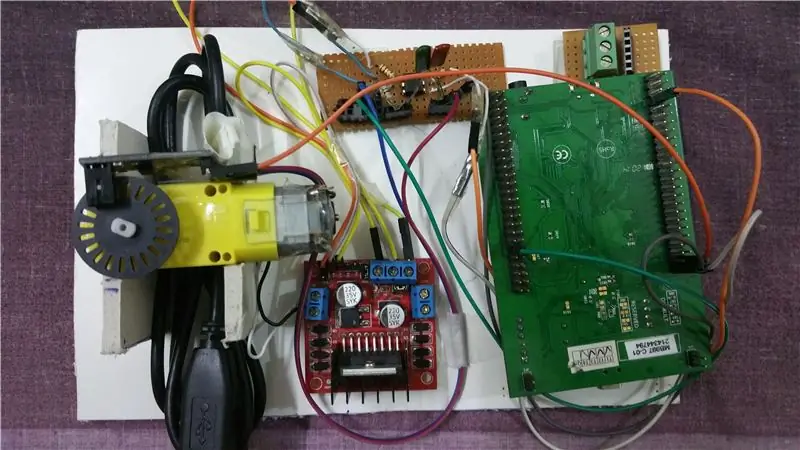

पीआईडी एल्गोरिथम (एसटीएम एमसी) का उपयोग करते हुए सेल्फ बैलेंसिंग रोबोट: 9 कदम

PID एल्गोरिथम (STM MC) का उपयोग करते हुए सेल्फ बैलेंसिंग रोबोट: हाल ही में वस्तुओं के सेल्फ बैलेंसिंग में बहुत काम किया गया है। आत्म संतुलन की अवधारणा उल्टे पेंडुलम के संतुलन से शुरू हुई। यह अवधारणा हवाई जहाजों के डिजाइन के लिए भी विस्तारित हुई। इस परियोजना में, हमने एक छोटा सा मोड तैयार किया है

PID एल्गोरिथम (STM32F4) का उपयोग करके DC मोटर का गति नियंत्रण: 8 चरण (चित्रों के साथ)

पीआईडी एल्गोरिदम (एसटीएम 32 एफ 4) का उपयोग कर डीसी मोटर का गति नियंत्रण: सभी को नमस्कार, यह एक अन्य परियोजना के साथ ताहिर उल हक है। इस बार यह MC के रूप में STM32F407 है। यह मध्य सेमेस्टर परियोजना का अंत है। आशा है कि आपको यह पसंद आया होगा। इसके लिए बहुत सारी अवधारणाओं और सिद्धांतों की आवश्यकता होती है, इसलिए हम पहले इसमें जाते हैं। कंप्यूटरों के आगमन के साथ और