विषयसूची:

- चरण 1: एर्नी के लिए विवाडो में एक परियोजना की स्थापना

- चरण 2: विवाडो में एर्नी का पीडब्लूएम बनाना

- चरण 3: विवाडो में एर्नी का टीडीओए बनाना

- चरण 4: एर्नी को लपेटना और निर्यात करना

- चरण 5: बिल्डिंग एर्नी

- चरण 6: एर्नी की पहली बसपा

- चरण 7: फ्रीआरटीओएस'इंग एर्नी

- चरण 8: एर्नी का सी कोड आयात करना

- चरण 9: डिबगिंग एर्नी

- चरण 10: एर्नी को स्वायत्त बनाना

- चरण 11: एर्नी प्यारा बनाना

वीडियो: How to Make Ernie: 11 Steps

2024 लेखक: John Day | [email protected]. अंतिम बार संशोधित: 2024-01-30 09:19

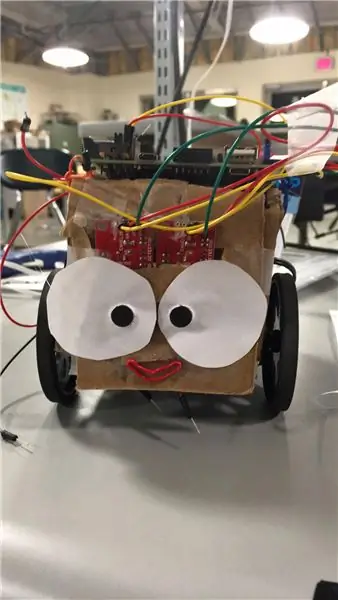

यह एक ज़ीबो बोर्ड का उपयोग करके रोबोट के बाद आपकी स्वायत्त ध्वनि एर्नी बनाने का एक ट्यूटोरियल है। यह कैसे कवर करेगा: विवाडो में एक प्रोजेक्ट बनाएं, एफपीजीए में पीडब्लूएम-जैसे सर्वो मोटर ड्राइवर बनाएं, दो ध्वनि सेंसर के साथ इंटरफेस, आगमन आईपी का समय अंतर बनाएं, फ्रीआरटीओएस का उपयोग करें, और बैटरी पैक से ज़ीबो चलाएं। कैल पॉली एसएलओ में रीयल टाइम ऑपरेटिंग सिस्टम क्लास (सीपीई 439) के लिए यह हमारी अंतिम परियोजना थी।

उपकरण सूची:

- 1 - ZYBO Zynq 7000 विकास बोर्ड

- 2 - लंबन सतत रोटेशन सर्वो

- 2 - साउंड सेंसर (स्पार्कफन साउंड डिटेक्टर)

- 1 - 5 वी लिथियम आयन यूएसबी बैटरी पैक (बोर्ड के लिए)

- 4 - एए बैटरी (सर्वो के लिए)

- 1 - AA बैटरी पैक (w/4 बैटरी स्लॉट)

- 1 - माइक्रो यूएसबी केबल

- 1 - ब्रेडबोर्ड

- कई - पुरुष से पुरुष तार

- 1 - सर्वो चेसिस

सॉफ़्टवेयर आवश्यकताएं:

- Xilinx Vivado Design Suite 2016.2

- मेहनती निपुण 2.16.1

चरण 1: एर्नी के लिए विवाडो में एक परियोजना की स्थापना

- एक जादूगर पॉप अप होगा

- अगला पर क्लिक करें

-

प्रोजेक्ट का अगला नाम

- कभी भी प्रोजेक्ट नाम या निर्देशिका पथ का उपयोग न करें जिसमें रिक्त स्थान हों !!!!!

- यह एक आरटीएल परियोजना होगी।

- हम स्रोत निर्दिष्ट नहीं करना चाहते हैं

-

नेक्स्ट पर क्लिक करने पर हम पार्ट पेज पर पहुंच जाते हैं। हम ZYNQ XC7Z010-1CLG400C का उपयोग कर रहे हैं।

- विवाडो में ज़ीबो को इसके पूर्व-परिभाषित बोर्डों में से एक के रूप में सूचीबद्ध नहीं किया गया है। चुनें: "पार्ट्स" फिर xc7z010clg400-1 खोजें।

- यदि आप गलती से गलत हिस्सा चुनते हैं तो आप आसानी से चिप्स स्विच कर सकते हैं: टूल्स -> प्रोजेक्ट सेटिंग्स -> सामान्य और "प्रोजेक्ट डिवाइस" के दाईं ओर डॉट्स पर क्लिक करें।

-

ब्लॉक डिज़ाइन बनाएँ पर क्लिक करें।

इसे अभी के लिए design_1 नाम दें

- आपको एक हरे रंग की पट्टी दिखाई देगी जो कहती है कि आईपी जोड़ें, इसे क्लिक करें।

-

Zynq के लिए खोजें।

- ZYNQ7 प्रोसेसिंग सिस्टम पर डबल क्लिक करें,

- यह ब्लॉक हमारे ब्लॉक डिजाइन में दिखाई देगा।

- आपको एक हरे रंग की पट्टी दिखाई देगी जो कहती है कि रन ब्लॉक ऑटोमेशन, इसे क्लिक करें।

- नीचे zybo_zynq_def.xml डाउनलोड करें।

-

विवाडो में, "XPS सेटिंग्स आयात करें" पर क्लिक करें और "zybo_zynq_def.xml" चुनें

यह प्री विवाडो ब्लॉक कॉन्फ़िगरेशन को ज़ीबो बोर्ड के सभी बिल्ट-इन पेरिफेरल्स और पिन असाइनमेंट के साथ पॉप्युलेट करता है।

-

ZYNQ ब्लॉक पर डबल क्लिक करें।

-

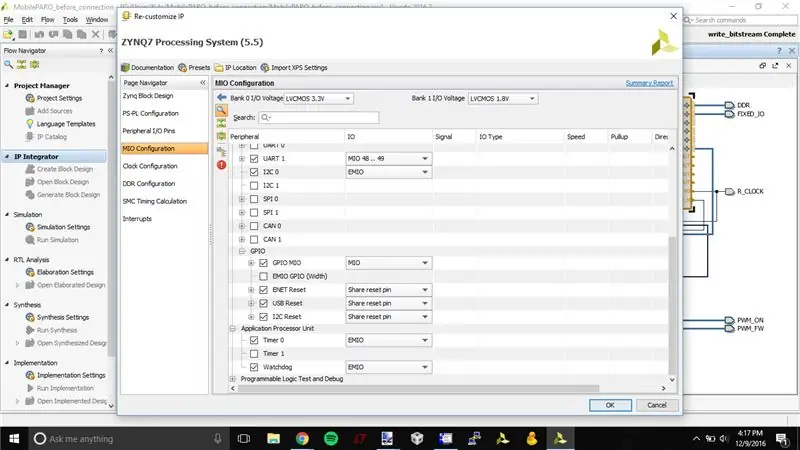

एमआईओ कॉन्फ़िगरेशन

- टाइमर 0 सक्षम करें (एप्लिकेशन प्रोसेसर यूनिट के तहत - img 1)

- वॉचडॉग सक्षम करें (एप्लिकेशन प्रोसेसर यूनिट के अंतर्गत- img 1)

- GPIO->GPIO MIO सक्षम करें (एप्लिकेशन प्रोसेसर यूनिट के अंतर्गत - img 2)

- GPIO->ENET रीसेट सक्षम करें (I/O पेरिफेरल्स के अंतर्गत- img 2)

-

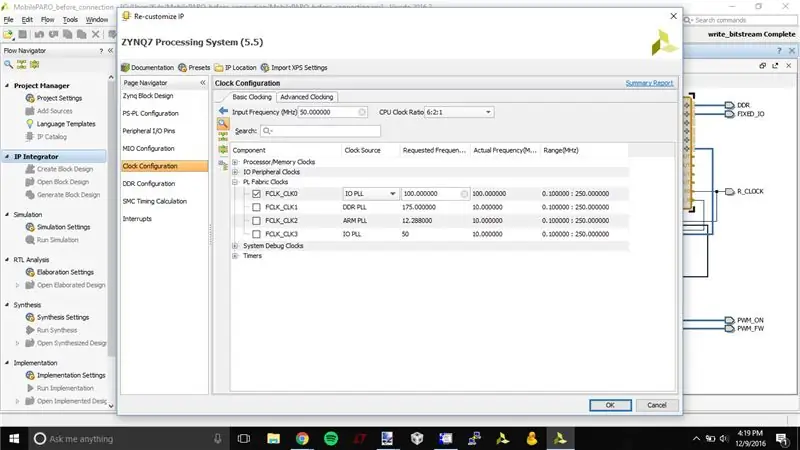

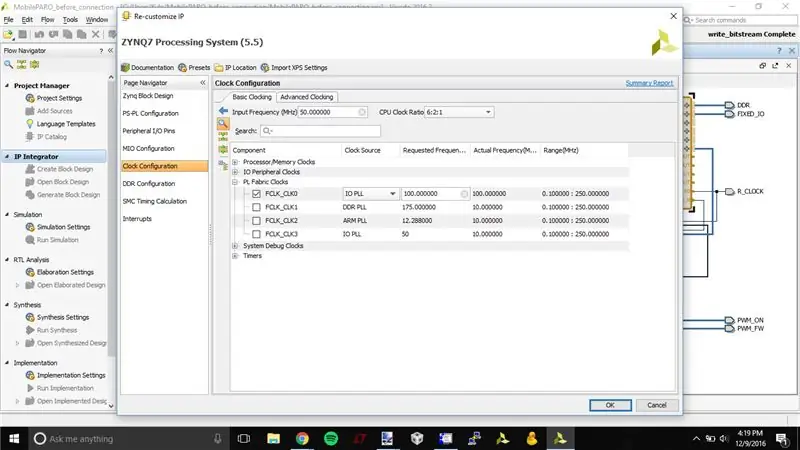

घड़ी विन्यास

FCLK0 अक्षम करें (PL फैब्रिक घड़ियों के अंतर्गत - img 3)

-

- ओके पर क्लिक करें।

-

अब "ब्लॉक ऑटोमेशन चलाएँ"।

संकेतों के बारे में कुछ प्रश्न होंगे, मान लीजिए OK

-

"एचडीएल रैपर जेनरेट करें" पर क्लिक करें।

उपयोगकर्ता संपादन की अनुमति देने के लिए हम जेनरेट किए गए रैपर की प्रतिलिपि बनाना चाहेंगे।

- ओके पर क्लिक करें।

चरण 2: विवाडो में एर्नी का पीडब्लूएम बनाना

यह चरण AXI लाइब्रेरी के माध्यम से भेजे गए इनपुट के साथ एक PWM IP उत्पन्न करेगा।

-

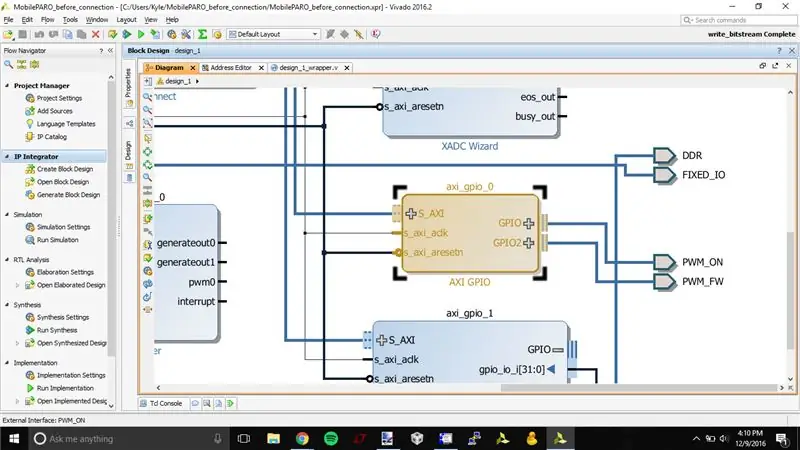

पृष्ठभूमि पर राइट-क्लिक करके और "आईपी जोड़ें" पर क्लिक करके AXI GPIO ब्लॉक बनाएं।

सर्च बार में "AXI_GPIO" टाइप करें, और इस पैकेज को चुनें

-

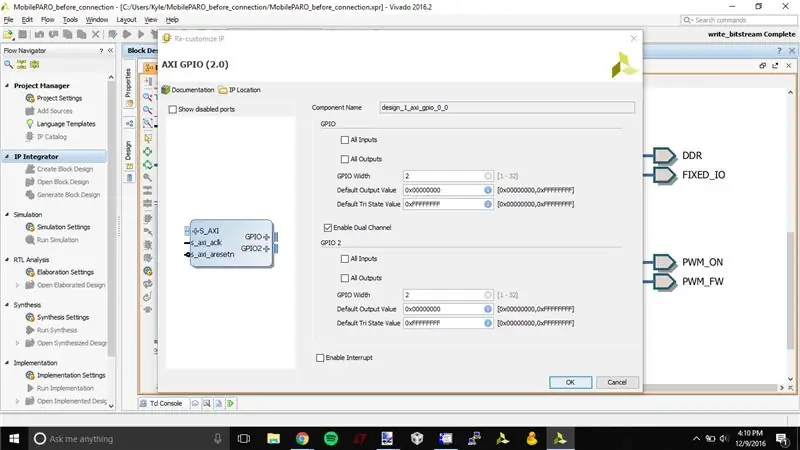

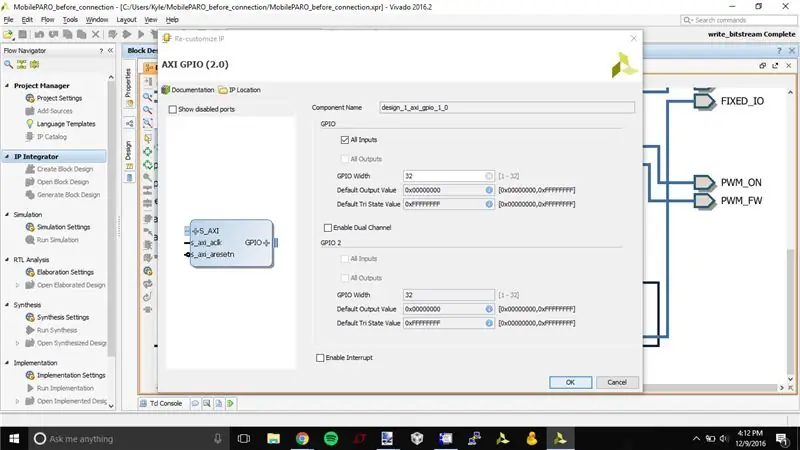

नए axi_gpio_0 ब्लॉक पर डबल-क्लिक करके IP को फिर से कस्टमाइज़ करें

- GPIO के तहत, GPIO की चौड़ाई 2 पर सेट करें। ये बिट्स प्रत्येक PWM मॉड्यूल इंस्टेंस को चलाने के लिए PWM_ON सिग्नल होंगे।

- "दोहरी चैनल सक्षम करें" पर क्लिक करें

- GPIO 2 के तहत, GPIO की चौड़ाई 2 पर सेट करें। ये बिट्स प्रत्येक PWM मॉड्यूल इंस्टेंस की दिशा निर्धारित करने के लिए PWM_FW सिग्नल होंगे।

-

GPIO लेबल वाले axi_gpio_0 आउटपुट पोर्ट पर राइट क्लिक करें, और "मेक एक्सटर्नल" चुनें

- GPIO लेबल वाले नए आउटपुट पर क्लिक करें, और बाएं टूलबार पर "गुण" टैब पर नेविगेट करें, और नाम बदलकर PWM_ON करें

- GPIO2 लेबल वाले नए आउटपुट पर क्लिक करें, और बाएं टूलबार पर "गुण" टैब पर नेविगेट करें, और नाम बदलकर PWM_FW करें

-

ब्लॉक डायग्राम के ऊपर हरे बैनर में रन कनेक्शन ऑटोमेशन चुनें।

यदि आप पोर्ट को मैन्युअल रूप से कनेक्ट करते हैं, तो हो सकता है कि AXI पतों को कॉन्फ़िगर न किया गया हो, जिसके कारण बाद में संचार संबंधी समस्याएं हो सकती हैं

-

फ्लो नेविगेटर फलक में, प्रोजेक्ट मैनेजर चुनें -> एक नया कस्टम आईपी ब्लॉक बनाने के लिए स्रोत जोड़ें

- "डिज़ाइन स्रोत जोड़ें या बनाएं" चुनें, और अगला हिट करें

- "फ़ाइल बनाएँ" पर क्लिक करें, फ़ाइल प्रकार को "SystemVerilog" में बदलें, और फ़ाइल नाम फ़ील्ड में "pwm" टाइप करें, फिर ठीक पर क्लिक करें

- समाप्त क्लिक करें

-

ओके दबाकर मॉड्यूल परिभाषित करें विंडो को अनदेखा करें (हम इन्हें बाद में अधिलेखित कर देंगे)

यदि यह पूछता है कि क्या आप निश्चित हैं, तो हाँ पर क्लिक करें

-

स्रोत टैब में, pwm.sv ("डिज़ाइन स्रोत/डिज़ाइन_1_wrapper" में स्थित) पर डबल-क्लिक करें।

नीचे संलग्न pwm.txt फ़ाइल से संपूर्ण SystemVerilog कोड को कॉपी/पेस्ट करें

चरण 3: विवाडो में एर्नी का टीडीओए बनाना

यह चरण एक TDOA IP उत्पन्न करेगा जिसका आउटपुट AXI लाइब्रेरी के माध्यम से पढ़ा जा सकता है

-

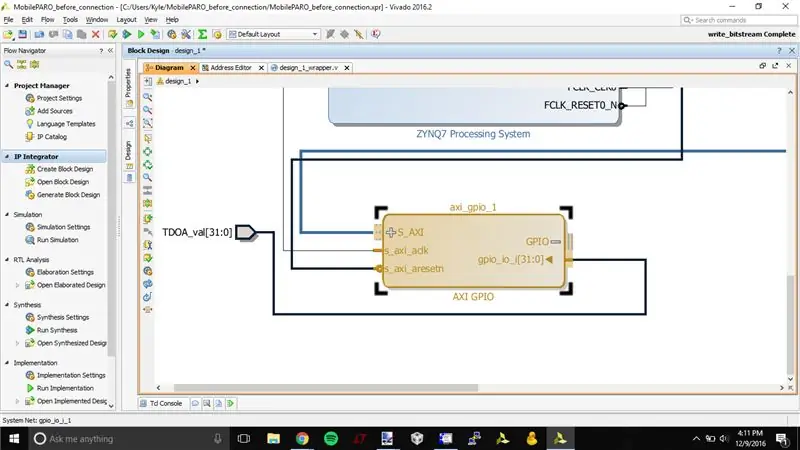

पृष्ठभूमि पर राइट-क्लिक करके और "आईपी जोड़ें" पर क्लिक करके AXI GPIO ब्लॉक बनाएं।

सर्च बार में "AXI_GPIO" टाइप करें, और इस पैकेज को चुनें

-

नए axi_gpio_1 ब्लॉक पर डबल-क्लिक करके IP को फिर से कस्टमाइज़ करें

- GPIO के तहत, "सभी इनपुट" बॉक्स को चेक करें, और GPIO की चौड़ाई 32 पर सेट करें। यह बस दो सेंसर के बीच आगमन के समय का अंतर होगी।

- axi_gpio_1 ब्लॉक के अंदर, gpio_io_i [३१:०] प्रकट करने के लिए GPIO पोर्ट के आगे + पर क्लिक करें।

-

gpio_io_i[३१:०] लेबल वाले axi_gpio_1 आउटपुट पोर्ट पर राइट क्लिक करें, और "बाहरी बनाएं" चुनें

gpio_io_i[३१:०] लेबल वाले नए इनपुट पर क्लिक करें, और बाएं टूलबार पर "गुण" टैब पर नेविगेट करें, और नाम को TDOA_val में बदलें

-

ब्लॉक डायग्राम के ऊपर हरे बैनर में रन कनेक्शन ऑटोमेशन चुनें।

यदि आप पोर्ट को मैन्युअल रूप से कनेक्ट करते हैं, तो हो सकता है कि AXI पतों को कॉन्फ़िगर न किया गया हो, जिसके कारण बाद में संचार संबंधी समस्याएं हो सकती हैं

-

फ्लो नेविगेटर फलक में, प्रोजेक्ट मैनेजर चुनें -> एक नया कस्टम आईपी ब्लॉक बनाने के लिए स्रोत जोड़ें

- "डिज़ाइन स्रोत जोड़ें या बनाएं" चुनें, और अगला हिट करें

- "फ़ाइल बनाएँ" पर क्लिक करें, फ़ाइल प्रकार को "SystemVerilog" में बदलें, और फ़ाइल नाम फ़ील्ड में "tdoa" टाइप करें, फिर ठीक पर क्लिक करें

- समाप्त क्लिक करें

-

ओके दबाकर मॉड्यूल परिभाषित करें विंडो को अनदेखा करें (हम इन्हें बाद में अधिलेखित कर देंगे)

यदि यह पूछता है कि क्या आप निश्चित हैं, तो हाँ पर क्लिक करें

-

स्रोत टैब में, tdoa.sv ("डिज़ाइन स्रोत/डिज़ाइन_1_wrapper" में स्थित) पर डबल-क्लिक करें।

नीचे संलग्न tdoa.txt फ़ाइल से संपूर्ण SystemVerilog कोड को कॉपी/पेस्ट करें

चरण 4: एर्नी को लपेटना और निर्यात करना

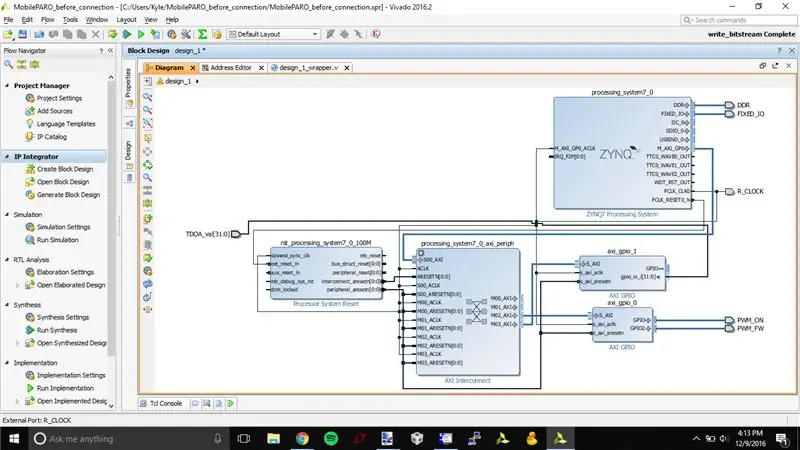

- सत्यापित करें कि ब्लॉक आरेख संलग्न स्क्रीनशॉट की तरह दिखता है

-

स्रोत टैब में, design_1.bd राइट-क्लिक करें और "HDL Wrapper बनाएं…" चुनें

- "उपयोगकर्ता संपादन की अनुमति देने के लिए उत्पन्न आउटपुट कॉपी करें" चुनें, फिर "ओके" दबाएं

- नीचे संलग्न design_1_wrapper.txt से कोड को कॉपी करें, और इसे जेनरेट किए गए design_1_wrapper.v कोड के स्थान पर पेस्ट करें

- डिज़ाइन सहेजें_1_wrapper.v

-

स्रोत टैब में, ZYBO_Master.xdc फ़ाइल को Constraints/constrs1 के अंतर्गत डबल-क्लिक करें

- नीचे संलग्न ZYBO_Master.txt से कोड को कॉपी करें, और मौजूदा ZYBO_Master.xdc कोड के स्थान पर पेस्ट करें

-

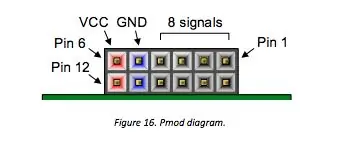

निम्नलिखित इनपुट/आउटपुट पिनों पर ध्यान दें:

- L15: बाईं मोटर के लिए PWM सिग्नल (Zybo पर Pmod JA2)

- L14: सही मोटर के लिए PWM सिग्नल (Zybo पर Pmod JA8)

- V12: साउंड सेंसर 1 से गेट इनपुट (Zybo पर Pmod JE1)

- K16: साउंड सेंसर 2 से गेट इनपुट (Zybo पर Pmod JE2)

-

फ्लो नेविगेटर पेन में, प्रोग्राम और डीबग के तहत "जेनरेट बिटस्ट्रीम" पर क्लिक करें

अगर आपको लगता है कि यह तुरंत हो गया है, तो शायद ऐसा नहीं है। गंभीरता से, कुछ चाय बनाओ

-

फ़ाइल-> निर्यात-> हार्डवेयर उत्पन्न करें पर क्लिक करें

"बिटस्ट्रीम शामिल करें" चेक करें और ओके दबाएं

- फ़ाइल पर क्लिक करें-> एसडीके लॉन्च करें

चरण 5: बिल्डिंग एर्नी

- सर्वो को सर्वो चेसिस पर माउंट करें।

-

सर्वो के लिए डेटाशीट के बाद, निम्न कार्य करें:

- Zybo के JA Pmod पर सर्वो के ग्राउंड को ग्राउंड पिन से कनेक्ट करें (संलग्न पिनआउट इमेज देखें)

-

सर्वो के पावर पिन को AA बैटरी पैक से कनेक्ट करें

हमने पाया कि जब सर्वो को Zybo के Vdd से जोड़ा जाता है, तो बोर्ड बहुत अधिक करंट खींचता है, जिससे बोर्ड लगातार रीसेट होता रहता है।

- इनपुट सिग्नल पिन को Zybo के उपयुक्त आउटपुट पिन से कनेक्ट करें (बाएं: JA2, दाएं: JA8)

- ध्वनि संवेदकों को चेसिस के सामने की ओर, आगे की ओर, उन्हें जितना संभव हो सके एक साथ रखते हुए माउंट करें

-

ध्वनि सेंसर को एकीकृत करने के लिए ध्वनि संवेदक के हुकअप मार्गदर्शिका का उपयोग करें

- प्रत्येक ध्वनि संवेदक के जमीन और Vdd पिन को जमीन पर तार दें और Zybo के JE Pmod पर Vdd पिन लगाएं (संलग्न पिनआउट छवि देखें)

- बाएं ध्वनि संवेदक के गेट पिन को JE1. से तार दें

- सही साउंड सेंसर के गेट पिन को JE2. से तार करें

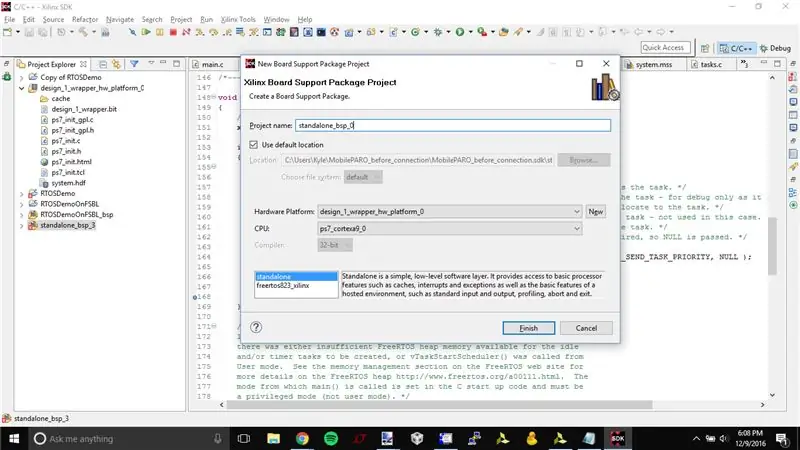

चरण 6: एर्नी की पहली बसपा

-

हमारे द्वारा अभी-अभी बनाए गए प्लेटफॉर्म को समेटने के लिए एक बसपा बनाएं।

आप इसे फ़ाइल -> नया -> बोर्ड सहायता पैकेज के माध्यम से प्राप्त कर सकते हैं।

-

बसपा बनाने में आपकी मदद करने के लिए एक विजार्ड पॉप अप होगा।

- हम इस बसपा को अपने मंच से जोड़ना चाहते हैं जिसे हमने अभी बनाया है, इसलिए

- हार्डवेयर प्लेटफॉर्म को हमारे द्वारा अभी बनाए गए प्लेटफॉर्म के अनुरूप होना चाहिए (देखें img 1)

- हमारा सीपीयू _0 सीपीयू होगा।

- समाप्त क्लिक करें

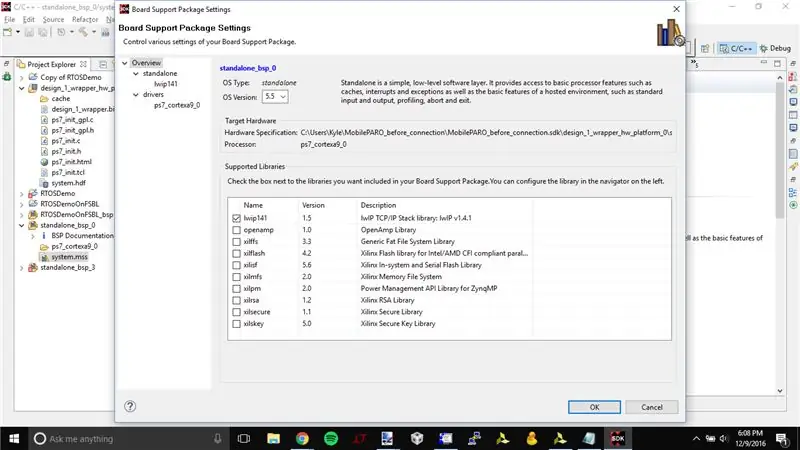

- पॉप अप विंडो में अपने bsp के साथ शामिल करने के लिए lwip141 को चेक करना सुनिश्चित करें (देखें img 2)

चरण 7: फ्रीआरटीओएस'इंग एर्नी

-

सोर्सफोर्ज से नवीनतम फ्रीआरटीओएस रिलीज डाउनलोड करें।

यदि डाउनलोड एक निष्पादन योग्य है, तो इसे अपनी प्रोजेक्ट निर्देशिका में फ्रीआरटीओएस फाइलों को निकालने के लिए चलाएं।

- उस एसडीके को खुला रखें, और फ़ाइल -> आयात पर क्लिक करें।

- हम सामान्य-> एक मौजूदा कार्यक्षेत्र से क्लिक करना चाहते हैं, और फिर हम उस स्थान पर नेविगेट करना चाहेंगे जहां हमने फ्रीआरटीओएस डाउनलोड किया था।

-

हमारा डेमो फ्रीआरटीओएस/डेमो/CORTEX_A9_Zynq_ZC702 में स्थित होगा। इस फ़ोल्डर का चयन करने पर, हमें तीन प्रोजेक्ट पॉप अप (हमारा कोड (ओएस), यह बीएसपी, और एचडब्ल्यू प्लेटफॉर्म) देखना चाहिए।

केवल अपने वर्तमान कार्यक्षेत्र में RTOSDemo आयात करें।

-

सभी "ब्लू" फ़ोल्डर प्रोजेक्ट्स पर संदर्भित बीएसपी को बदलें

- राइट क्लिक करके और "संदर्भित बीएसपी बदलें" का चयन करें।

- बसपा का चयन करें जिसे आपने अभी-अभी अपने Zybo. के लिए बनाया है

- Xilinx के SDK ब्लू फोल्डर में कोड एडिटिंग वास्तविक कोड प्रोजेक्ट हैं।

चरण 8: एर्नी का सी कोड आयात करना

- RTOSDemo/src निर्देशिका में, मौजूदा main.c को यहाँ संलग्न main.c फ़ाइल के साथ अधिलेखित करें।

- main_sound.c फ़ाइल को RTOSDemo/src निर्देशिका में कॉपी करें।

चरण 9: डिबगिंग एर्नी

- रन चुनें -> डिबग कॉन्फ़िगरेशन

- बाएँ फलक पर एक नया सिस्टम डीबगर रन बनाएँ

-

लक्ष्य सेटअप टैब में,

"संपूर्ण सिस्टम रीसेट करें" चुनें ताकि वह और ps7_init दोनों चयनित हों

-

अब एप्लिकेशन टैब चुनें।

- "डाउनलोड एप्लिकेशन" चुनें

- कॉर्टेक्सा9_0 कोर को "प्रोग्राम एंट्री पर रोकें" पर सेट करें

- लागू करें और डीबग करें पर क्लिक करें।

- सत्यापित करें कि डिबगिंग प्रक्रिया में कोई त्रुटि नहीं है

- रोबोट पर कड़ी नजर रखते हुए, रिज्यूमे बटन को तब तक दबाएं जब तक कि प्रोग्राम बिना किसी ब्रेकप्वाइंट को हिट किए न चला जाए

- रोबोट को अब मुड़ना चाहिए और तेज आवाज की ओर बढ़ना चाहिए। वाह!

चरण 10: एर्नी को स्वायत्त बनाना

- एक बार जब आपका प्रोजेक्ट जाने के लिए तैयार हो जाता है (आप डिबगर के माध्यम से बिना किसी समस्या के चल सकते हैं) तो आप इसे अपने बोर्ड पर फ्लैश मेमोरी में लोड करने के लिए तैयार हैं।

-

जिसे "फर्स्ट स्टेज बूट लोडर" (FSBL) प्रोजेक्ट कहा जाता है, उसे बनाएं और स्टार्टअप पर आपकी प्रोजेक्ट फ़ाइलों (बिट स्ट्रीम और OS) को लोड करने के लिए आपके बोर्ड को आवश्यक सभी निर्देश शामिल करें।

- चुनें: फ़ाइल-> नया-> एप्लिकेशन प्रोजेक्ट और निम्न विंडो दिखाई देनी चाहिए।

- आप जो चाहते हैं उसे नाम दें (यानी "एफएसबीएल")

- सुनिश्चित करें कि हार्डवेयर प्लेटफॉर्म वही है जिसके साथ आप काम कर रहे हैं

- अगला दबाएं (समाप्त न दबाएं)

- Zynq FSBL टेम्प्लेट चुनें

- समाप्त क्लिक करें।

- एक बार निर्माण प्रक्रिया पूरी हो जाने पर आपको पता चल जाएगा कि क्या प्रोजेक्ट एक्सप्लोरर विंडो में निम्नलिखित दो नए फ़ोल्डर्स देखने पर सब कुछ काम कर गया है।

-

बूट इमेज बनाएं अब आपको बूट इमेज बनानी होगी।

- अपने प्रोजेक्ट फ़ोल्डर पर राइट क्लिक करें (इस मामले में मेरा "RTOSDemo" कहा जाता है)

- ड्रॉप डाउन से “क्रिएट बूट इमेज” पर क्लिक करें

-

यदि सब कुछ सही ढंग से जुड़ा हुआ है, तो प्रोजेक्ट को पता चल जाएगा कि उसे किन फाइलों की जरूरत है और निम्न विंडो दिखाई देगी जैसा कि आप नीचे देख रहे हैं (कुंजी यह है कि आपके पास बूट छवि अनुभाग के तहत 3 विभाजन हैं, बूटलोडर, आपकी बिट फ़ाइल, और आपकी परियोजनाएं.elf फ़ाइल)

यदि ऐसा नहीं है तो संभवतः आपके प्रोजेक्ट लिंकिंग में कुछ गड़बड़ है। सुनिश्चित करें कि परियोजना फ़ोल्डर उनके संबंधित बसपा से जुड़े हुए हैं

- "छवि बनाएं" बटन पर क्लिक करें

-

सॉफ़्टवेयर में प्रदर्शन करने का अंतिम चरण अब अपनी पहले से बनाई गई छवि को बोर्ड की मेमोरी में फ्लैश करना है

- एसडीके के मुख्य टूल बार से चुनें Xilinx Tools->Program Flash Memory

- सुनिश्चित करें कि सही हार्डवेयर प्लेटफॉर्म चुना गया है और छवि फ़ाइल पथ पिछले चरण में बनाई गई. BIN फ़ाइल को सही ढंग से इंगित कर रहा है।

- फ़्लैश प्रकार से "qspi सिंगल" चुनें

- अखंडता का बीमा करने के लिए "फ़्लैश के बाद सत्यापित करें" पर टिक करें लेकिन इसकी आवश्यकता नहीं है

- अपने बोर्ड को कॉन्फ़िगर करें अंत में आपको यह सुनिश्चित करने की आवश्यकता है कि जब BootROM चलाया जाता है तो बोर्ड प्रोग्रामिंग मोड जम्पर (JP5) qspi (जिसमें आपने अभी-अभी फ्लैश किया है) से बूट करने के लिए चयन करने के लिए सही ढंग से सेट किया गया है।

- अब बस डिवाइस को पावर साइकल करें और सुनिश्चित करें कि "लॉजिक कॉन्फिगरेशन डन एलईडी" (एलईडी 10) हरे रंग की रोशनी में है।

चरण 11: एर्नी प्यारा बनाना

- फर

- बहुत सारे फर

- बड़ी आँखें!

- … लंबा टोप

सिफारिश की:

How to Make Mareografo: 5 Steps

How to Make Mareografo: O JSN-SR04T ये है सेंसर अल्ट्रासैनिको डे डिस्टेंशिया। उसरेमोस एसएसई सेंसर अल्ट्रासैनिको पैरा मेदिर ए डिस्टेंसिया एंट्रे ओ डेक ई ए अगुआ। नेस्ट ट्यूटोरियल, वोक एप्रेंडर कोमो यूसर निबंध सेंसर कॉम ओ अर्डुइनो, पैरा कॉन्स्ट्रुइर उम मारेओग्राफो। ए डिस्टेंसिया एंट्रे ओ डी

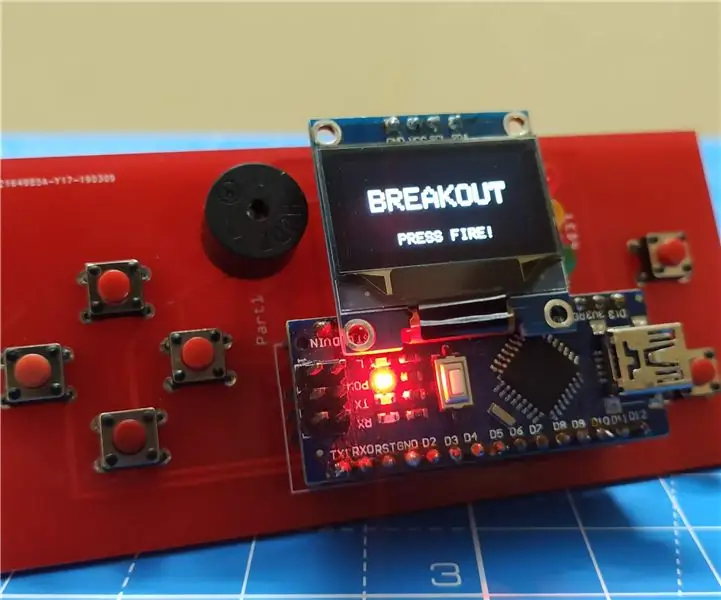

How to Make Arduboy: 6 Steps

How to Make Arduboy: इस लेख में आप देखेंगे कि Arduino Nano का उपयोग करके मिनी गेमबॉय कैसे बनाया जाता है। इसे Arduboy भी कहा जाता है। Arduboy एक हैंडहेल्ड गेम कंसोल है जिसमें ओपन सोर्स सॉफ्टवेयर है, जो Arduino हार्डवेयर प्लेटफॉर्म पर आधारित है। इसे बनाते हैं

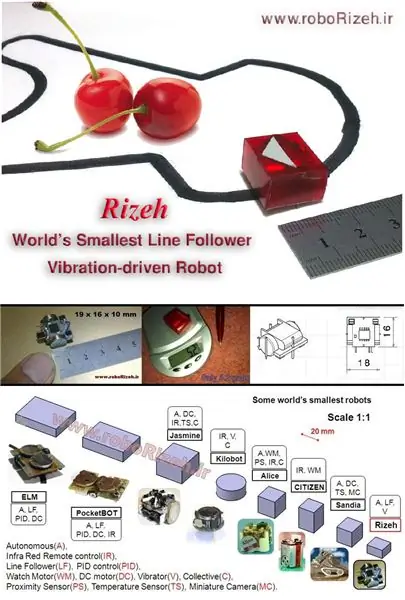

How to Make World's Smallest Line Follower Robot (robo Rizeh): 7 Steps (चित्रों के साथ)

How to Make World’s Smallest Line Follower Robot (robo Rizeh): How to create दुनिया का सबसे छोटा लाइन फॉलोअर रोबोट (vibrobot) "roboRizeh" वजन: ५जीआर आकार: १९x१६x१० मिमी द्वारा: नघी सोतौदेह शब्द "रिज़ेह" एक फारसी शब्द है जिसका अर्थ है "छोटा"। Rizeh एक कंपन आधारित बहुत छोटा ro है

How to make इंडोनेशिया's WajanBolic या PanciBolic (USB): 6 Steps

इंडोनेशिया का वजानबोलिक या पैन्सीबॉलिक (USB) कैसे बनाएं: मेरा तीसरा निर्देश! अब मैं आपको वोक से बने इंडोनेशिया के सभी वाईफाई एंटीना सिखाने जा रहा हूं। नोट: मैंने इस बढ़िया चीज़ का आविष्कार नहीं किया

Techduino -- How to Make your खुद Homemade Arduino Uno R3--: 9 Steps (चित्रों के साथ)

Techduino || अपना खुद का घर का बना Arduino Uno R3 कैसे बनाएं ||: यदि आप मेरे जैसे हैं, जब मैंने अपना Arduino प्राप्त किया और अपनी पहली चिप पर एक अंतिम प्रोग्रामिंग की, तो मैं इसे अपने Arduino Uno R3 से खींचना चाहता था और इसे रखना चाहता था मेरे अपने सर्किट पर। यह भविष्य की परियोजनाओं के लिए मेरे Arduino को भी मुक्त कर देगा। बहुत कुछ पढ़ने के बाद