विषयसूची:

- चरण 1: एसपीआई का अवलोकन

- चरण 2: डिजाइन निर्दिष्टीकरण

- चरण 3: प्रारंभ करना

- चरण 4: एसपीआई मास्टर कोर और सिमुलेशन वेवफॉर्म का आरटीएल व्यू

वीडियो: वीएचडीएल में एसपीआई मास्टर का डिजाइन: 6 चरण

2024 लेखक: John Day | [email protected]. अंतिम बार संशोधित: 2024-01-30 09:21

इस निर्देश में, हम VHDL में खरोंच से एक SPI बस मास्टर डिजाइन करने जा रहे हैं।

चरण 1: एसपीआई का अवलोकन

- SPI एक सिंक्रोनस सीरियल बस है

- इसकी लोकप्रियता और सादगी ने इसे धारावाहिक संचार में एक वास्तविक मानक बना दिया है

- फुल-डुप्लेक्स बस

- सरल प्रोटोकॉल और सबसे तेज़ सीरियल बस में

चरण 2: डिजाइन निर्दिष्टीकरण

ये SPI मास्टर के विनिर्देश हैं जिन्हें हम डिज़ाइन करने वाले हैं:

- संचालन के सभी चार तरीकों का समर्थन करता है; गतिशील रूप से विन्यास योग्य

- बिजली की बचत के लिए घड़ी सक्षम नियंत्रण

- स्थिर रूप से विन्यास योग्य शब्द लंबाई और गति

- ट्रांसमिशन और रिसेप्शन दोनों के लिए सिंगल इंटरप्ट

चरण 3: प्रारंभ करना

सबसे पहले, हमारे आईपी में दो इंटरफेस होने चाहिए। एक सीरियल इंटरफ़ेस है और दूसरा समानांतर इंटरफ़ेस है। सीरियल इंटरफ़ेस में SPI के वास्तविक मानक संकेत होते हैं: MOSI, MISO, SS, SCLK।

MOSI को कभी SDO कहा जाता है और MISO को कभी SDI कहा जाता है।

सीरियल इंटरफ़ेस का उपयोग बाहरी बाह्य उपकरणों यानी SPI स्लेव के साथ संचार करने के लिए किया जाता है।

समानांतर इंटरफ़ेस का उपयोग हमारे होस्ट यानी एक माइक्रोकंट्रोलर या माइक्रोप्रोसेसर के साथ संचार करने के लिए किया जाता है, जो वास्तव में मास्टर को बताता है कि सीरियल लाइनों के माध्यम से किस डेटा को क्रमिक रूप से प्रसारित और प्राप्त किया जाना है। यानी, सभी डेटा बसें समानांतर इंटरफ़ेस से संबंधित हैं।

हमारे पास एक वैश्विक घड़ी है जो आंतरिक SPI तर्क, साथ ही SCLK को चलाती है, जिसे हम आंतरिक रूप से उत्पन्न करते हैं।

हमारे पास कुछ कंट्रोल सिग्नल भी हैं जैसे राइट इनेबल, क्लॉक इनेबल। और इंटरप्ट और अन्य स्थिति संकेत।

चूंकि हमें जटिल नियंत्रण स्थितियों से निपटना होता है, ऐसे सीरियल संचार आईपी को एफएसएम के रूप में डिजाइन करना आसान होता है। हम एसपीआई मास्टर को एफएसएम के रूप में भी डिजाइन करेंगे। FSM को एक अन्य आंतरिक घड़ी द्वारा संचालित किया जाएगा जो SCLK का दो गुना है। वह आंतरिक घड़ी वैश्विक घड़ी से तुल्यकालिक काउंटरों का उपयोग करके उत्पन्न होती है।

सभी नियंत्रण संकेत जो क्रॉस क्लॉक डोमेन में सुरक्षित पक्ष पर होने के लिए सिंक्रोनाइज़र हैं।

चरण 4: एसपीआई मास्टर कोर और सिमुलेशन वेवफॉर्म का आरटीएल व्यू

यह बिना किसी समर्पित FPGA IP के उपयोग किया गया एक नंगे RTL डिज़ाइन है। इसलिए यह किसी भी FPGA के लिए पूरी तरह से पोर्टेबल कोड है।

सिफारिश की:

VHDL में I2C मास्टर का डिज़ाइन: 5 चरण

VHDL में I2C मास्टर का डिज़ाइन: इस निर्देश में, VHDL में एक साधारण I2C मास्टर को डिज़ाइन करने पर चर्चा की गई है। नोट: पूर्ण छवि देखने के लिए प्रत्येक छवि पर क्लिक करें

वीएचडीएल और वेरिलोग में एक साधारण वीजीए नियंत्रक का डिजाइन: 5 कदम

VHDL और Verilog में एक साधारण VGA नियंत्रक का डिज़ाइन: इस निर्देश में, हम RTL में एक साधारण VGA नियंत्रक डिज़ाइन करने जा रहे हैं। वीजीए कंट्रोलर डिजिटल सर्किट है जिसे वीजीए डिस्प्ले को चलाने के लिए डिज़ाइन किया गया है। यह फ्रेम बफर (वीजीए मेमोरी) से पढ़ता है जो प्रदर्शित किए जाने वाले फ्रेम का प्रतिनिधित्व करता है, और आवश्यक

वीएचडीएल में यूएआरटी का डिजाइन: 5 कदम

VHDL में UART का डिज़ाइन: UART का मतलब यूनिवर्सल एसिंक्रोनस रिसीवर ट्रांसमीटर है। यह सबसे लोकप्रिय और सरल धारावाहिक संचार प्रोटोकॉल है। इस निर्देश में, आप सीखेंगे कि VHDL में UART मॉड्यूल कैसे डिज़ाइन किया जाए

वीएचडीएल में मास्टरमाइंड गेम: 3 चरण

वीएचडीएल में मास्टरमाइंड गेम: हमारे प्रोजेक्ट के लिए, हमने “मास्टरमाइंड” VHDL में गेम बेसिस3 बोर्ड पर खेला जाएगा। मास्टरमाइंड पारंपरिक रूप से खूंटे और एक गेम बोर्ड के साथ खेला जाने वाला एक कोड-ब्रेकिंग गेम है। खिलाड़ी 4 की एक पंक्ति में मिश्रित रंगों के खूंटे रखता है

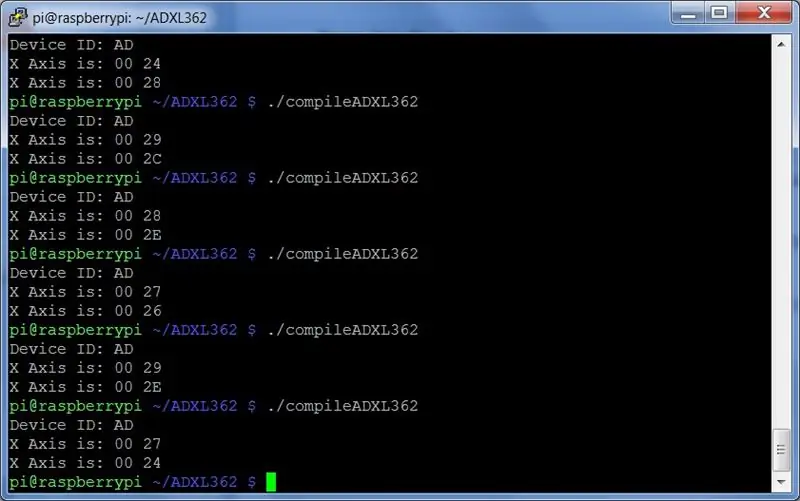

प्रारंभिक* पाई पर एसपीआई: रास्पबेरी पाई का उपयोग करते हुए एसपीआई 3-अक्ष एक्सेलेरोमीटर के साथ संचार करना: 10 कदम

प्रारंभिक* पाई पर एसपीआई: रास्पबेरी पाई का उपयोग करके एसपीआई 3-अक्ष एक्सेलेरोमीटर के साथ संचार बहुत प्रारंभिक… मुझे भौतिक हुकअप की बेहतर तस्वीरें जोड़ने और कुछ अजीब कोड के माध्यम से काम करने की आवश्यकता है