विषयसूची:

- चरण 1: सिद्धांत

- चरण 2: सामग्री और उपकरण

- चरण 3: वायरिंग और हार्डवेयर सेटअप

- चरण 4: वीएचडीएल सेटअप (विवाडो)

- चरण 5: कोड डाउनलोड

वीडियो: बेसिस३ एफपीजीए डिजिटल ऑडियो सिंथेसाइज़र: ५ कदम

2024 लेखक: John Day | [email protected]. अंतिम बार संशोधित: 2024-01-30 09:23

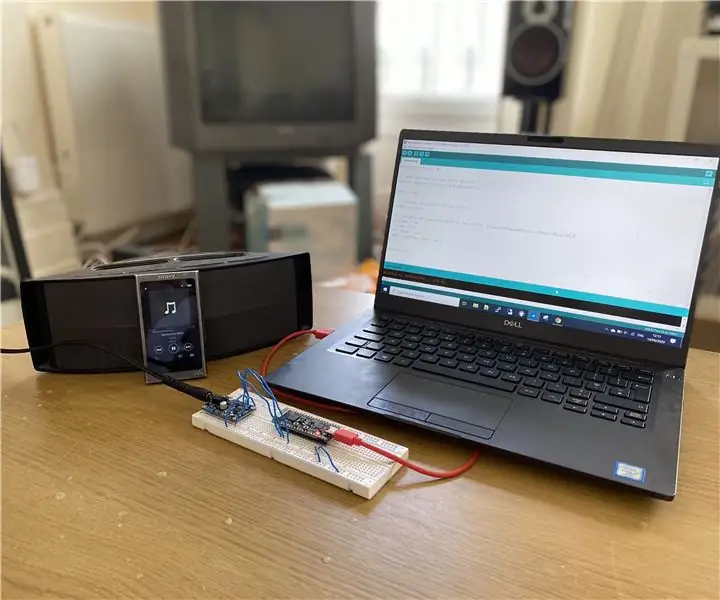

यह डिजिटल साइन वेव कीबोर्ड सिंथेसाइज़र कीबोर्ड की तरह लगाए गए क्षणिक स्विच की एक श्रृंखला के माध्यम से उपयोगकर्ता इनपुट लेगा और स्पीकर के माध्यम से ऑडियो तरंग आउटपुट करेगा। उपयोगकर्ता इनपुट के आधार पर, डिवाइस C4 से C6 तक विभिन्न आवृत्तियों की साइन तरंगें उत्पन्न करेगा। उपयोगकर्ता C4 से C6 (कुल 25 नोट) तक, और एक ही समय में अधिकतम चार कुंजियों को इनपुट कर सकता है - यदि चार से अधिक कुंजियों को दबाया जाता है, तो चार निम्नतम स्वर बजाए जाएंगे।

यह प्रोजेक्ट हमारे कैल पॉली सीपीई 133 डिजिटल डिज़ाइन क्लास के लिए रयान मॉरिस और माविस त्सोई द्वारा किया गया था:)

चरण 1: सिद्धांत

एक FPGA बोर्ड केवल डिजिटल सिग्नल आउटपुट कर सकता है। दूसरे शब्दों में, यह केवल उच्च (3.3V) वोल्टेज या कम (0V) वोल्टेज उत्पन्न कर सकता है। हालाँकि, ऑडियो सिग्नल एनालॉग होते हैं और वोल्टेज में असीम रूप से कई वृद्धि हो सकती है। इसके आस-पास जाने के लिए, हम एक एनालॉग तरंग का अनुकरण करने के लिए PWM (पल्स चौड़ाई मॉड्यूलेशन) सिग्नल का उपयोग करेंगे। यदि आप नहीं जानते कि पीडब्लूएम क्या है, तो इसे देखें:

चरण 2: सामग्री और उपकरण

- विवाडो के साथ कंप्यूटर स्थापित

- हम विवाडो संस्करण 2017.2. का उपयोग करेंगे

- बेसिस३ एफपीजीए बोर्ड

- 25 SPDT सीमा स्विच (हमने इनका उपयोग किया)

- 30 जम्पर तार (एक छोर पुरुष, दूसरा छोर कोई फर्क नहीं पड़ता), 12 इंच

- वायर कटर

- वायर स्ट्रिपर्स

- सोल्डरिंग के लिए अतिरिक्त तार

- राल-कोर मिलाप

- सोल्डरिंग आयरन

- ”महिला ऑडियो जैक

- एम्पलीफायर / स्पीकर

- स्विच को चालू करने के लिए कुछ (हमने प्रोटोबार्ड + लकड़ी के बक्से का इस्तेमाल किया)

चरण 3: वायरिंग और हार्डवेयर सेटअप

सिस्टम आर्किटेक्चर

चित्र 1 देखें: 25 उपलब्ध इनपुट → बेसिस3 बोर्ड → एम्पलीफायर और स्पीकर।

उत्पादन

चित्र 2 देखें: बेसिस3 बोर्ड → 1/2 महिला ऑडियो जैक → स्पीकर (एम्पलीफायर के साथ)

इनपुट

कम इनपुट देखने के लिए बेसिस3 बोर्ड पर पीएमओडी कनेक्शन जमीन से जुड़ा होना चाहिए और खुले सर्किट के रूप में छोड़े जाने पर ठीक से काम नहीं करेगा। इस वजह से, हमें अपनी सभी नोट कुंजियों के लिए SPDT स्विच का उपयोग करना पड़ता है। एक एसपीडीटी स्विच मूल रूप से उपयोगकर्ता को दबाए जाने पर सर्किट के बीच स्विच करने की अनुमति देता है, इसलिए हम बेसिस 3 बोर्ड को कम (0V) या उच्च (3.3V) सिग्नल इनपुट करने के लिए उन्हें हमारे "बटन" के रूप में उपयोग करेंगे।

प्रत्येक स्विच में 3.3V से जुड़ा NO (सामान्य रूप से खुला) टर्मिनल, GND से जुड़ा NC (सामान्य रूप से बंद) टर्मिनल और FPGA इनपुट से जुड़ा COM (सामान्य) टर्मिनल होगा। चित्र 3 देखें।

क्योंकि हमारे पास 25 सीमा स्विच हैं, वे सभी एक सामान्य 3.3V लाइन और एक सामान्य GND लाइन साझा करेंगे। फिर, प्रत्येक सीमा स्विच से सिग्नल लाइन को 8 के समूहों में बंडल किया जाएगा और हमारे द्वारा किए जाने वाले स्मारकीय गड़बड़ी को कम करने के लिए ज़िप करने योग्य जम्पर तारों का उपयोग करके बेसिस 3 बोर्ड पर पीएमओडी कनेक्शन से जोड़ा जाएगा। चित्र 4 या पहली आठ कुंजियों का उदाहरण देखें।

चरण 4: वीएचडीएल सेटअप (विवाडो)

साइन वेव जनरेटर और पीडब्लूएम जनरेटर का परीक्षण पहले यह सुनिश्चित करने के लिए किया गया था कि हमारी अवधारणा काम करती है, फिर इनपुट लिमिटर और आयाम योजक / शिफ्ट को एकीकृत किया गया। प्रत्येक प्रक्रिया ब्लॉक के फ़ंक्शन और I/O का विवरण चित्र में दिखाया गया है। कोड नीचे दिखाया गया है, लेकिन VHD और txt फ़ाइलों के रूप में भी संलग्न है। यदि विसंगतियां हैं, तो वीएचडी फाइलों के साथ जाएं।

BTW: हमें शायद अपनी लाइनों को छोटा करना चाहिए था, लेकिन इंस्ट्रक्शंस पर कोड एम्बेड करना भी इससे निपटने के लिए काफी कष्टप्रद निकला, इसलिए रिक्ति सबसे बड़ी नहीं है और कोई सिंटैक्स हाइलाइटिंग नहीं है। यदि आपके पास विवाडो है और आप कोड का पालन करना चाहते हैं, तो हम अत्यधिक अनुशंसा करते हैं कि आप केवल फ़ाइल डाउनलोड करें।

सबसे पहले, आइए साइन वेव जेनरेटर मॉड्यूल को देखें।

पुस्तकालय IEEE; IEEE. STD_LOGIC_1164. ALL का उपयोग करें; IEEE. NUMERIC_STD. ALL का उपयोग करें; इकाई Wave_Generator पोर्ट है (ट्रिगर: STD_LOGIC में; - कुंजी दबाएं Freq_Cnt: STD_LOGIC_VECTOR में (15 डाउनटू 0); - काउंटर वैल्यू = 100 मेगाहर्ट्ज / (नोट फ्रीक्वेंसी * साइन वेव के 64 डिवीजन) (निकटतम संख्या में गोल) - नाम बदला गया Freq wavegenCLK से: STD_LOGIC में; --Basys3 100MHz CLK वेवऑट: STD_LOGIC_VECTOR (9 डाउनटू 0) से बाहर); - वेव एंड वेव_जेनरेटर का हस्ताक्षरित आयाम; वास्तुकला Wave_Generator का व्यवहार संकेत है I: पूर्णांक श्रेणी 0 से 64: = 0; - आयाम मेमोरी बैंक प्रकार का सूचकांक मेमोरी_टाइप पूर्णांक श्रेणी -64 से 63 की सरणी (0 से 63) है; - आयाम मान रखने के लिए मेमोरी बैंक (ROM) बनाएं - क्या यह RAM या ROM बस सोच रहा है … सिग्नल आयाम: मेमोरी_टाइप: = (0, 7, 13, 19, 25, 30, 35, 40, 45, 49, 52, 55, 58, 60, 62, 63, 63, 63, 62, 60, 58, 55, 52, 49, 45, 40, 35, 30, 25, 19, 13, 7, 0, -7, -13, -19, -25, -30, -35, -40, -45, -49, -52, -55, -58, -60, -62, -63, -63, -63, -62, - 60, -58, -55, -52, -49, -45, -40, -35, -30, -25, -19, -13, -7)); - साइन वेव स्टार्ट प्रोसेस के लिए आयाम मेमोरी बैंक (वेवजेनसीएलके, ट्रिगर) वैरिएबल काउंटर: अहस्ताक्षरित (15 डाउनटू 0): = to_unsigned (0, 16); - क्लॉक डिवाइडर काउंटर, काउंट 1 से नाम बदलकर शुरू होता है अगर (राइजिंग_एज (वेवजेनसीएलके)) तो अगर (ट्रिगर = '1') तो - कुंजी को काउंटर दबाया जाता है: = काउंटर + 1; अगर (काउंटर = अहस्ताक्षरित (Freq_Cnt)) तो - Freq_Cnt = 100Mhz / (नोट फ्रीक * साइन वेव के 64 डिवीजन) - काउंटर को रीसेट करें और आउटपुट काउंटर को आयाम डेटा असाइन करें: = to_unsigned (0, 16); वेवऑट <= STD_LOGIC_VECTOR (to_signed(आयाम (i), 10)); - वेतन वृद्धि मैं अगले पढ़ने के लिए मैं <= i + 1; -- रीसेट i अगर एक साइन वेव पूरा हो गया है अगर (i = ६३) तो i <= ०; अगर अंत; अगर अंत; -- (काउंटर = अहस्ताक्षरित (Freq_Cnt)) अन्य -- कुंजी दबाया नहीं गया -- आउटपुट रीसेट करें, आयाम सूचकांक, और काउंटर वेवऑट <= "0000000000"; मैं <= 0; काउंटर: = to_unsigned (0, 16); --आउटपुट आयाम = -64 जब कोई नोट नहीं खेला जाता है तो समाप्त होता है; -- (ट्रिगर = '1') समाप्त हो तो; - (राइजिंग_एज (सीएलके)) अंतिम प्रक्रिया; अंत व्यवहार;

हम आंतरिक घड़ी और एक ROM का उपयोग करके Basys3 में एक डिजिटल साइन तरंग उत्पन्न करेंगे। यह ROM 64 मानों को संग्रहीत करेगा जो साइन तरंग पर 64 आयामों का प्रतिनिधित्व करते हैं। चित्र 1 देखें। हम जिन 64 मानों का उपयोग करते हैं, वे बहुत अच्छे रिज़ॉल्यूशन के साथ साइन वेव का अनुकरण करते हैं।

आंतरिक घड़ी का उपयोग करते हुए, हम उस मान की गणना करते हैं जो घड़ी की गति को उस तरंग की आवृत्ति से विभाजित करता है जिसे हम चाहते हैं और 64: Clk div = 100MHz / (Freq * 64) हर बार जब हमारा काउंटर उस मान तक पहुंचता है, तो हम एक नंबर पर कॉल करते हैं ROM और इसे हमारे वेव जनरेटर मॉड्यूल से भेजें। हमारी तरंग की आवृत्ति इस बात पर निर्भर करेगी कि हम इन आयामों को कितनी तेजी से कहते हैं।

हमारे पास 25 उप-मॉड्यूल होंगे, प्रत्येक एक आवृत्ति/नोट से जुड़े होंगे।

साइन वेव जेनरेटर मॉड्यूल को कॉल करने वाले शेष कोड यहां दिए गए हैं:

पुस्तकालय IEEE; IEEE. STD_LOGIC_1164. ALL का उपयोग करें; IEEE. NUMERIC_STD. ALL का उपयोग करें; इकाई Two_Octave_Synth पोर्ट है (CLK: STD_LOGIC में; O4: STD_LOGIC_VECTOR में (11 डाउनटू 0); O5: STD_LOGIC_VECTOR(12 डाउनटू 0); आउटपुट: STD_LOGIC से बाहर); दो_ऑक्टेव_सिंथ समाप्त करें; वास्तुकला Two_Octave_Synth का व्यवहार घटक है Wave_Generator पोर्ट है (ट्रिगर: STD_LOGIC में; Freq_Cnt: STD_LOGIC_VECTOR में (15 से 0 तक); wavegenCLK: STD_LOGIC में; वेवआउट: STD_LOGIC_VECTOR से बाहर (9 डाउनटू 0)); अंत घटक; ----------------------- तरंग जनरेटर से आउटपुट सिग्नल ---------------------- ----- सिग्नल WaveC4, WaveCs4, WaveD4, WaveDs4, WaveE4, WaveF4, WaveFs4, WaveG4, WaveGs4, WaveA4, WaveAs4, WaveB4, WaveC5, WaveCs5, WaveD5, WaveDs5, WaveE5, WaveF5, WaveFs5, WaveG5, WaveGs5, WaveA5, WaveAs5, WaveB5, WaveC6: हस्ताक्षरित (9 डाउनटू 0); --------------------------------- नोट चयन तर्क के लिए-------------- ------ सिग्नल C4, Cs4, D4, Ds4, E4, F4, Fs4, G4, Gs4, A4, As4, B4, C5, Cs5, D5, Ds5, E5, F5, Fs5, G5, Gs5, A5, एएस 5, बी 5, सी 6: अहस्ताक्षरित (4 डाउनटू 0); सिग्नल cntC4, cntCs4, cntD4, cntDs4, cntE4, cntf4, cntFs4, cntG4, cntGs4, cntA4, cntAs4, cntB4, cntC5, cntCs5, cntD5, cntDs5, cntE5, cntF5, cntfs5, gst5, cnt5, cnt5, cnt5, cnt5, cnt5, cnt5,: अहस्ताक्षरित (4 डाउनटू 0); संकेत त्रुटि: STD_LOGIC; ----------------------------------- साइन वेव्स जोड़ने के लिए---------- --------------- सिग्नल वेव0, वेव1, वेव2, वेव3: हस्ताक्षरित (9 डाउनटू 0); - वेव जेनरेटर मॉड्यूल आउटपुट सिग्नल वेवसम से सिग्नल: एसटीडी_LOGIC_VECTOR(9 डाउनटू 0); - संक्षेप में साइन तरंगों के लिए संकेत (2 की तारीफ -512 से 511) सकारात्मक तरंग संकेत: एसटीडी_LOGIC_VECTOR(9 डाउनटू 0); --अहस्ताक्षरित 0 से 1023, PWM जनरेटर में उपयोग के लिए ----------------------------------- PWM उत्पन्न करने के लिए ----------------------------- सिग्नल पिंग_लेंथ: अहस्ताक्षरित (9 डाउनटू 0): = अहस्ताक्षरित (पॉजिटिववेवसम); - सिग्नल ऑफ_लेंथ: अहस्ताक्षरित (6 डाउनटू 0): = to_unsigned (127, 7) - अहस्ताक्षरित (वेव); सिग्नल पीडब्लूएम: अहस्ताक्षरित (9 डाउनटू 0):= to_unsigned(0, 10); प्रारंभ Note_C4: Wave_Generator पोर्ट मैप (ट्रिगर => O4(0), Freq_Cnt => X"1755", wavegenCLK => CLK, हस्ताक्षरित (WaveOut) => WaveC4); --5973, 261.63 हर्ट्ज Note_Cs4: Wave_Generator पोर्ट मैप (ट्रिगर => O4(1), Freq_Cnt => X"1606", wavegenCLK => CLK, साइन (वेवऑट) => WaveCs4);--5638, 277.18 हर्ट्ज Note_D4: Wave_Generator पोर्ट मैप (ट्रिगर => O4 (2), Freq_Cnt => X "14C9", wavegenCLK => CLK, हस्ताक्षरित (WaveOut) => WaveD4); --5321, 293.66 हर्ट्ज Note_Ds4: Wave_Generator पोर्ट मैप (ट्रिगर => O4 (3), Freq_Cnt => X"139F", wavegenCLK => CLK, साइन (वेवऑट) => वेवडीएस 4);---5023, 311.13 हर्ट्ज Note_E4: Wave_Generator पोर्ट मैप (ट्रिगर => O4 (4), Freq_Cnt => X "1285", wavegenCLK => CLK, हस्ताक्षरित (WaveOut) => WaveE4); --4741, 329.63 हर्ट्ज Note_F4: Wave_Generator पोर्ट मैप (ट्रिगर => O4(5), Freq_Cnt => X"117B", wavegenCLK => CLK, हस्ताक्षरित (WaveOut) => WaveF4); --4475, 349.23 हर्ट्ज Note_Fs4: Wave_Generator पोर्ट मैप (ट्रिगर => O4(6), Freq_Cnt => X"1080", wavegenCLK => CLK, हस्ताक्षरित (WaveOut) => WaveFs4);--4224, 369.99 हर्ट्ज Note_G4: Wave_Generator पोर्ट मैप (ट्रिगर => O4 (7), Freq_Cnt => X "0F92", wavegenCLK => CLK, हस्ताक्षरित (WaveOut) => WaveG4); --3986, 392.00 हर्ट्ज Note_Gs4: Wave_Generator पोर्ट मैप (ट्रिगर => O4(8), Freq_Cnt => X"0EB3", wavegenCLK => CLK, हस्ताक्षरित (वेवऑट) => WaveGs4);--3763, 415.30 हर्ट्ज Note_A4: Wave_Generator पोर्ट मैप (ट्रिगर => O4(9), Freq_Cnt => X"0DE0", wavegenCLK => CLK, हस्ताक्षरित (WaveOut) => WaveA4); --3552, 440.00 हर्ट्ज Note_As4: Wave_Generator पोर्ट मैप (ट्रिगर => O4(10), Freq_Cnt => X"0D18", wavegenCLK => CLK, हस्ताक्षरित (वेवऑट) => WaveAs4);--3352, 466.16 हर्ट्ज Note_B4: Wave_Generator पोर्ट मैप (ट्रिगर => O4(11), Freq_Cnt => X"0C5C", wavegenCLK => CLK, हस्ताक्षरित (WaveOut) => WaveB4); --३१६४, ४९३.८८ हर्ट्ज ------------------------------------------ -------------------------------------------------- --------------------------- Note_C5: Wave_Generator पोर्ट मैप (ट्रिगर => O5(0), Freq_Cnt => X"0BAB", wavegenCLK => CLK, हस्ताक्षरित (WaveOut) => WaveC5); --२९८७, ५२३.२५ हर्ट्ज़ नोट_सीएस५: वेव_जेनरेटर पोर्ट मैप (ट्रिगर => ओ५(1), फ़्रीक_कंट => एक्स"0बी०३", वेवजेनसीएलके => सीएलके, हस्ताक्षरित (वेवऑट) => वेवसीएस५);--२८१९, ५५४.३७ हर्ट्ज़ नोट_डी५: Wave_Generator पोर्ट मैप (ट्रिगर => O5 (2), Freq_Cnt => X "0A65", wavegenCLK => CLK, हस्ताक्षरित (WaveOut) => WaveD5); --२६६१, ५८७.३३ हर्ट्ज Note_Ds5: Wave_Generator पोर्ट मैप (ट्रिगर => O5(3), Freq_Cnt => X"09D0", wavegenCLK => CLK, हस्ताक्षरित (WaveOut) => WaveDs5);---2512, 622.25 हर्ट्ज Note_E5: Wave_Generator पोर्ट मैप (ट्रिगर => O5 (4), Freq_Cnt => X "0943", wavegenCLK => CLK, हस्ताक्षरित (WaveOut) => WaveE5); --२३७१, ६५९.२५ हर्ट्ज़ Note_F5: Wave_Generator पोर्ट मैप (ट्रिगर => O5(5), Freq_Cnt => X"08Be", wavegenCLK => CLK, हस्ताक्षरित (WaveOut) => WaveF5); --2238, 698.46 हर्ट्ज Note_Fs5: Wave_Generator पोर्ट मैप (ट्रिगर => O5(6), Freq_Cnt => X"0840", wavegenCLK => CLK, हस्ताक्षरित (WaveOut) => WaveFs5);--2112, 739.99 हर्ट्ज Note_G5: Wave_Generator पोर्ट मैप (ट्रिगर => O5(7), Freq_Cnt => X"07CA", wavegenCLK => CLK, हस्ताक्षरित (WaveOut) => WaveG5); - १९९४, ७८३.९९ हर्ट्ज़ नोट_जीएस५: वेव_जेनरेटर पोर्ट मैप (ट्रिगर => ओ५(८), फ्रीक_कंट => एक्स"०७५ए", वेवजेनसीएलके => सीएलके, हस्ताक्षरित (वेवऑट) => वेवजीएस५);--१८८२, ८३०.६१ हर्ट्ज नोट_ए५: Wave_Generator पोर्ट मैप (ट्रिगर => O5(9), Freq_Cnt => X"06F0", wavegenCLK => CLK, हस्ताक्षरित (WaveOut) => WaveA5); --1776, 880.00 हर्ट्ज Note_As5: Wave_Generator पोर्ट मैप (ट्रिगर => O5(10), Freq_Cnt => X"068C", wavegenCLK => CLK, हस्ताक्षरित (वेवऑट) => WaveAs5);---1676, 932.33 हर्ट्ज Note_B5: Wave_Generator पोर्ट मैप (ट्रिगर => O5(11), Freq_Cnt => X"062E", wavegenCLK => CLK, हस्ताक्षरित (WaveOut) => WaveB5); --1582, 987.77 हर्ट्ज Note_C6: Wave_Generator पोर्ट मैप (ट्रिगर => O5(12), Freq_Cnt => X"05D6", wavegenCLK => CLK, हस्ताक्षरित (WaveOut) => WaveC6); --1494, 1046.5 हर्ट्ज ------------ नोट चयन तर्क ------------- C4 <= "0000" और O4(0); Cs4 <= "0000" और O4(1); D4 <= "0000" और O4(2); Ds4 <= "0000" और O4(3); E4 <= "0000" और O4(4); F4 <= "0000" और O4(5); Fs4 <= "0000" और O4(6); G4 <= "0000" और O4(7); Gs4 <= "0000" और O4(8); A4 <= "0000" और O4(9); As4 <= "0000" और O4(10); B4 <= "0000" और O4(11); C5 <= "0000" और O5(0); Cs5 <= "0000" और O5(1); D5 <= "0000" और O5(2); Ds5 <= "0000" और O5(3); E5 <= "0000" और O5(4); F5 <= "0000" और O5(5); Fs5 <= "0000" और O5(6); G5 <= "0000" और O5(7); Gs5 <= "0000" और O5(8); A5 <= "0000" और O5(9); As5 <= "0000" और O5(10); B5 <= "0000" और O5(11); C6 <= "0000" और O5(12); सीएनटीसी4 <= सी4; cntCs4 <= C4 + Cs4; सीएनटीडी४ <= सी४ + सीएस४ + डी४; cntDs4 <= C4 + Cs4 + D4 + Ds4; cntE4 <= C4 + Cs4 + D4 + Ds4 + E4; cntF4 <= C4 + Cs4 + D4 + Ds4 + E4 + F4; cntFs4 <= C4 + Cs4 + D4 + Ds4 + E4 + F4 + Fs4; cntG4 <= C4 + Cs4 + D4 + Ds4 + E4 + F4 + Fs4 + G4; cntGs4 <= C4 + Cs4 + D4 + Ds4 + E4 + F4 + Fs4 + G4 + Gs4; cntA4 <= C4 + Cs4 + D4 + Ds4 + E4 + F4 + Fs4 + G4 + Gs4 + A4; cntAs4 <= C4 + Cs4 + D4 + Ds4 + E4 + F4 + Fs4 + G4 + Gs4 + A4 + As4; cntB4 <= C4 + Cs4 + D4 + Ds4 + E4 + F4 + Fs4 + G4 + Gs4 + A4 + As4 + B4; cntC5 <= C4 + Cs4 + D4 + Ds4 + E4 + F4 + Fs4 + G4 + Gs4 + A4 + As4 + B4 + C5; cntCs5 <= C4 + Cs4 + D4 + Ds4 + E4 + F4 + Fs4 + G4 + Gs4 + A4 + As4 + B4 + C5 + Cs5; cntD5 <= C4 + Cs4 + D4 + Ds4 + E4 + F4 + Fs4 + G4 + Gs4 + A4 + As4 + B4 + C5 + Cs5 + D5; cntDs5 <= C4 + Cs4 + D4 + Ds4 + E4 + F4 + Fs4 + G4 + Gs4 + A4 + As4 + B4 + C5 + Cs5 + D5 + Ds5; cntE5 <= C4 + Cs4 + D4 + Ds4 + E4 + F4 + Fs4 + G4 + Gs4 + A4 + As4 + B4 + C5 + Cs5 + D5 + Ds5 + E5; cntF5 <= C4 + Cs4 + D4 + Ds4 + E4 + F4 + Fs4 + G4 + Gs4 + A4 + As4 + B4 + C5 + Cs5 + D5 + Ds5 + E5 + F5; cntFs5 <= C4 + Cs4 + D4 + Ds4 + E4 + F4 + Fs4 + G4 + Gs4 + A4 + As4 + B4 + C5 + Cs5 + D5 + Ds5 + E5 + F5 + Fs5; cntG5 <= C4 + Cs4 + D4 + Ds4 + E4 + F4 + Fs4 + G4 + Gs4 + A4 + As4 + B4 + C5 + Cs5 + D5 + Ds5 + E5 + F5 + Fs5 + G5; cntGs5 <= C4 + Cs4 + D4 + Ds4 + E4 + F4 + Fs4 + G4 + Gs4 + A4 + As4 + B4 + C5 + Cs5 + D5 + Ds5 + E5 + F5 + Fs5 + G5 + Gs5; cntA5 <= C4 + Cs4 + D4 + Ds4 + E4 + F4 + Fs4 + G4 + Gs4 + A4 + As4 + B4 + C5 + Cs5 + D5 + Ds5 + E5 + F5 + Fs5 + G5 + Gs5 + A5; cntAs5 <= C4 + Cs4 + D4 + Ds4 + E4 + F4 + Fs4 + G4 + Gs4 + A4 + As4 + B4 + C5 + Cs5 + D5 + Ds5 + E5 + F5 + Fs5 + G5 + Gs5 + A5 + As5; cntB5 <= C4 + Cs4 + D4 + Ds4 + E4 + F4 + Fs4 + G4 + Gs4 + A4 + As4 + B4 + C5 + Cs5 + D5 + Ds5 + E5 + F5 + Fs5 + G5 + Gs5 + A5 + As5 + B5; cntC6 <= C4 + Cs4 + D4 + Ds4 + E4 + F4 + Fs4 + G4 + Gs4 + A4 + As4 + B4 + C5 + Cs5 + D5 + Ds5 + E5 + F5 + Fs5 + G5 + Gs5 + A5 + As5 + B5 + सी6; चयन: प्रक्रिया (WaveC4, WaveCs4, WaveD4, WaveDs4, WaveE4, WaveF4, WaveFs4, WaveG4, WaveGs4, WaveA4, WaveAs4, WaveB4, WaveC5, WaveCs5, WaveD5, WaveDs5, WaveE5, WaveF5, WaveFs5, WaveG5, WaveGs5, WaveA5, WaveAs5, WaveB5, WaveC6) अगर (cntC6 = "00000") से शुरू होता है तो --------------- अगर कोई सिग्नल उत्पन्न नहीं हो रहा है तो Wave0 <= "0000000000"; वेव1 <= "0000000000"; वेव 2 <= "0000000000"; वेव 3 <= "0000000000"; और अगर (O4(0) = '1') तो ------------------- नोट C4 ने वेव0 वेव0 वेव1 एरर वेव0 वेव1 वेव 2 एरर वेव0 वेव 1 वेव 2 वेव 3 एरर वेव 0 वेव 1 खेला। वेव2 वेव3 त्रुटि वेव0 वेव1 वेव2 वेव3 त्रुटि वेव0 वेव1 वेव2 वेव3 त्रुटि वेव0 वेव1 वेव2 वेव3 त्रुटि वेव0 वेव1 वेव2 वेव3 त्रुटि वेव0 वेव1 वेव2 वेव3 त्रुटि वेव 0 वेव 1 वेव 2 वेव 3 त्रुटि वेव 0 वेव 1 वेव 2 वेव 3 त्रुटि वेव 0 वेव 1 वेव 2 वेव 3 त्रुटि वेव 0 वेव 1 वेव 2 वेव 3 त्रुटि वेव 0 वेव 1 वेव2 वेव3 त्रुटि वेव0 वेव1 वेव2 वेव3 त्रुटि वेव0 वेव1 वेव2 वेव3 त्रुटि वेव0 वेव1 वेव2 वेव3 त्रुटि वेव0 वेव1 वेव2 वेव3 त्रुटि वेव0 वेव1 वेव2 वेव3 त्रुटि वेव 0 वेव 1 वेव 2 वेव 3 त्रुटि वेव 0 वेव 1 वेव 2 वेव 3 त्रुटि वेव 0 वेव 1 वेव 2 वेव 3 त्रुटि वेव 0 वेव 1 वेव 2 वेव 3 त्रुटि वेव 0 < = वेवसी6; वेव1 <= "0000000000"; वेव 2 <= "0000000000"; वेव3 वेव1 <= वेवसी6; वेव 2 <= "0000000000"; वेव3 वेव2 <= वेवसी6; Wave3 Wave3 त्रुटि Wave1 <= "0000000000"; वेव 2 <= "0000000000"; वेव3 वेव2 <= "0000000000"; Wave3 Wave3 त्रुटि <= '1'; अंतिम मामला; अगर अंत; अगर अंत; प्रक्रिया समाप्त; ------------- साइन वेव योजक ---------------------- वेवसम <= STD_LOGIC_VECTOR (वेव0 + वेव 1 + वेव 2 + वेव 3); ------------- pwm के लिए साइन वेव पॉजिटिव बनाएं--------------------- पॉजिटिववेवसम <= वेवसम (9) और वेवसम (8 डाउन टू 0 नहीं)); ------------- पीडब्लूएम जनरेटर--------------------- प्रक्रिया (सीएलके) --चर गणना: अहस्ताक्षरित (1 डाउनटू 0):= to_unsigned(0, 2); शुरू करें अगर (राइजिंग_एज (सीएलके)) तो --गिनती: = गिनती + 1; --if (गिनती = to_unsigned(4, 2)) तब --गिनती:= to_unsigned(0, 2); --if (PWM = to_ if (PWM <ping_length) तो आउटपुट <= '1'; अन्य आउटपुट <= '0'; अंत अगर; PWM <= PWM + 1; ping_length <= अहस्ताक्षरित (पॉजिटिववेवसम); --end अगर; अंत अगर; अंत प्रक्रिया; अंत व्यवहार;

4 नोट चयनकर्ता इस परियोजना का सबसे कठिन हिस्सा सिर्फ चार आवृत्तियों का चयन कर रहा है। हमने इसे पूरी तरह से IF स्टेटमेंट के साथ किया, और हमने वेरिएबल्स के बजाय सिग्नल का उपयोग किया ताकि प्रक्रिया को सिम्युलेटेड और डीबग किया जा सके। हमने वेरिएबल और फॉर लूप का उपयोग करके अन्य तरीकों की कोशिश की, लेकिन रन-टाइम त्रुटियों में भाग गया। इसलिए, अंत में, हमने फैसला किया कि अगर यह काम करता है, तो हम इसे अकेला छोड़ देंगे।जो टूटा हुआ अमीरात नहीं है उसे ठीक न करें?

चार आउटपुट तरंगों को Wave0, Wave1, Wave2, Wave3 लेबल किया गया है - ये वे हैं जिन्हें अंतिम आउटपुट बनाने के लिए एक साथ जोड़ा जाएगा।

कोड को देखते हुए, आपको C4, Cs4, D4, Ds4, आदि लेबल वाले संकेतों का एक गुच्छा दिखाई देगा। ये 5-बिट सिग्नल हैं जो O4 (ऑक्टेव 4) या O5 (ऑक्टेव 5) से संबंधित ट्रिगर लेते हैं और उन्हें बनाते हैं। जोड़ने के लिए 5-बिट।

आगे cntC4, cntCs4, आदि वेरिएबल दर्शाते हैं कि लक्ष्य नोट सहित कितने नोट लक्ष्य नोट से कम खेले गए हैं। उदाहरण के लिए, यदि C4, E4, G4, A#4, और D5 बजाया जाता है (C9 कॉर्ड) cntC4 1 होगा, cntE4 2 होगा, cntG4 3 होगा, आदि।

फिर, जब भी कोई नोट बजाया जाता है, तो यह देखने के लिए लक्ष्य नोट की गिनती की जांच की जाएगी कि नोट सिग्नल को कहां तक लगाया जाए। उदाहरण के लिए, यदि D5 नोट चलाया जाता है (जिसका अर्थ है कि O5(2) ऊंचा है) और cntD5 3 है, तो वर्तमान में 3 नोट चल रहे हैं, जिसमें 2 नोट D5 से कम हैं, इसलिए हम waveD5 को Wave2 (तीसरी लहर) से जोड़ देंगे वेव0 से सिग्नल की गिनती)। वैकल्पिक रूप से, यदि cntD5 5 है, तो वर्तमान में 5 नोट चल रहे हैं, जिसमें 4 नोट D5 से कम हैं, इसलिए हम केवल waveD5 को लटका छोड़ देंगे और इसके साथ कुछ भी नहीं करेंगे।

सभी 25 नोटों के मामलों को कवर करने के लिए IF स्टेटमेंट को फिर दोहराया जाता है।

आयाम योजक

सबसे कम 4 तरंगों का चयन करने के बाद हमें उन्हें एक साथ जोड़ना होगा। कारण हम केवल चार नोट एक साथ जोड़ेंगे क्योंकि पीडब्लूएम विचार हम अपने आउटपुट के लिए उपयोग कर रहे हैं, केवल एक निश्चित संकल्प हो सकता है जब तक कि पीडब्लूएम बहुत धीमी गति से चल रहा हो और स्पीकर पीडब्लूएम स्क्वायर वेव को उठाना शुरू कर दे। उदाहरण के लिए, यदि हम 8192 (13 बिट) के रिज़ॉल्यूशन का उपयोग करते हैं, तो उन 8192 बिंदुओं में से प्रत्येक को ऑनबोर्ड घड़ी के बढ़ते किनारे के अनुरूप होना चाहिए। तो, 100MHz / 8192 = 12.2kHz, जो मानव श्रवण की सीमा के भीतर है।

एम्पलीट्यूड का वास्तविक जोड़ सुपर सरल है, आपको बस यह सुनिश्चित करना है कि यह वास्तव में तेजी से चल सके।

पीडब्लूएम आउटपुट

PWM का कर्तव्य चक्र उस पल में हमारे आउटपुट वेव के आयाम का प्रतिनिधित्व करेगा। उदाहरण के लिए, यदि हमारे पास ० से १२८ की आयाम सीमा है, तो ०% कर्तव्य चक्र होगा, ६४ ५०% होगा, १२८ १००% होगा, आदि। यह पीडब्लूएम बहुत तेजी से चलेगा (हमारा ९७.६ kHz है), इतनी तेजी से कि स्पीकर अलग-अलग वर्ग तरंगों को नहीं पहचान पाएगा और इसके बजाय औसत वोल्टेज को देखेगा, जिससे हमारा "एनालॉग" सिग्नल बन जाएगा।

बाधाओं फ़ाइल

हो सकता है कि आपने अपने हार्डवेयर को अलग तरीके से जोड़ा हो, इसलिए बस सुनिश्चित करें कि बाधा फ़ाइल मेल खाती है।

चरण 5: कोड डाउनलोड

विवाडो के लिए.txt प्रारूप और.vhd दोनों में कोड नीचे दिया गया है। Wave_Generator तरंग जनरेटर उप-मॉड्यूल है, और Two_Octave_Synth अन्य सभी चीज़ों के साथ शीर्ष मॉड्यूल है।

सिफारिश की:

ब्लूटूथ ऑडियो और डिजिटल सिग्नल प्रोसेसिंग: एक Arduino फ्रेमवर्क: 10 कदम

ब्लूटूथ ऑडियो और डिजिटल सिग्नल प्रोसेसिंग: एक Arduino फ्रेमवर्क: सारांश जब मैं ब्लूटूथ के बारे में सोचता हूं तो मैं संगीत के बारे में सोचता हूं लेकिन दुख की बात है कि अधिकांश माइक्रोकंट्रोलर ब्लूटूथ के माध्यम से संगीत नहीं चला सकते हैं। रास्पबेरी पाई कर सकता है लेकिन वह एक कंप्यूटर है। मैं ब्लूट के माध्यम से ऑडियो चलाने के लिए माइक्रोकंट्रोलर्स के लिए एक Arduino आधारित ढांचा विकसित करना चाहता हूं

मोजो एफपीजीए विकास बोर्ड शील्ड: 3 चरण

मोजो एफपीजीए डेवलपमेंट बोर्ड शील्ड: इस शील्ड के साथ अपने मोजो डेवलपमेंट बोर्ड को बाहरी इनपुट से कनेक्ट करें। मोजो डेवलपमेंट बोर्ड क्या है? मोजो डेवलपमेंट बोर्ड Xilinx spartan 3 FPGA पर आधारित एक डेवलपमेंट बोर्ड है। बोर्ड Alchitry द्वारा बनाया गया है। FPGA बहुत उपयोगी हैं

वीएचडीएल और बेसिस3 बोर्ड का उपयोग कर बुनियादी स्टॉपवॉच: 9 कदम

VHDL और Basys3 बोर्ड का उपयोग करके बेसिक स्टॉपवॉच: बेसिक VHDL और बेसिस 3 बोर्ड का उपयोग करके स्टॉपवॉच कैसे बनाएं, इस निर्देश में आपका स्वागत है। हम आपके साथ अपनी परियोजना साझा करने के लिए उत्साहित हैं! यह पतन २०१६ में कैल पॉली, एसएलओ में पाठ्यक्रम सीपीई १३३ (डिजिटल डिजाइन) के लिए एक अंतिम परियोजना थी। हम जिस परियोजना का निर्माण कर रहे हैं

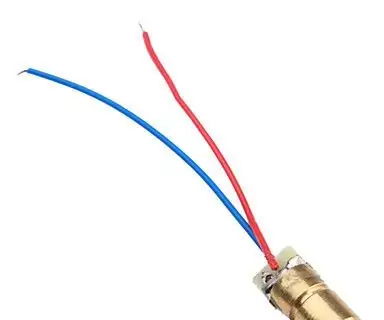

सरल और सस्ता लेजर डिजिटल ऑडियो ट्रांसमिशन: 4 कदम

सरल और सस्ता लेजर डिजिटल ऑडियो ट्रांसमिशन: जब से मैंने लेजर गन बनाई है, मैं ऑडियो भेजने के लिए लेजर को मॉड्यूलेट करने के बारे में सोच रहा हूं, या तो मनोरंजन के लिए (बच्चों के लिए इंटरकॉम), या शायद अधिक परिष्कृत लेजर गन के लिए डेटा संचारित करने के लिए। , एक रिसीवर को यह पता लगाने में सक्षम करता है कि उसे किसके द्वारा मारा गया था।

कस्टम सिल्वर केबल्स ऑडियो/डिजिटल/उच्च आवृत्ति/जीपीएस: 7 कदम

कस्टम सिल्वर केबल्स ऑडियो/डिजिटल/उच्च आवृत्ति/जीपीएस: कई नए ऑडियो/वीडियो मोड और नए उपकरणों के साथ, आइपॉड के लिए ऑडियो और अब वीडियो के लिए डिजिटल दोनों के साथ हमें अपने सिस्टम को अधिक जटिल केबल वाले नए उपकरणों से जोड़ना होगा। कुछ बहुत महँगे… इनमें अवयव अवश्य होने चाहिए & निर्माण परियोजना के लिए सामग्री