विषयसूची:

- आपूर्ति

- चरण 1: अपनी पसंद के पीसीबी निर्माता को Gerber अपलोड करें

- चरण 2: बोर्ड असेंबली

- चरण 3: सॉफ्टवेयर सेटअप

वीडियो: मोजो एफपीजीए विकास बोर्ड शील्ड: 3 चरण

2024 लेखक: John Day | [email protected]. अंतिम बार संशोधित: 2024-01-30 09:20

इस शील्ड के साथ अपने मोजो डेवलपमेंट बोर्ड को बाहरी इनपुट से कनेक्ट करें।

मोजो डेवलपमेंट बोर्ड क्या है?

Mojo विकास बोर्ड Xilinx spartan 3 FPGA पर आधारित एक विकास बोर्ड है। बोर्ड Alchitry द्वारा बनाया गया है। एफपीजीए बहुत उपयोगी होते हैं जहां एक साथ कई प्रक्रियाओं को निष्पादित किया जाना चाहिए।

आपको क्या चाहिए होगा?

आपूर्ति

मोजो विकास बोर्ड

गेरबर फ़ाइल

8 x 15k ओम रेसिस्टर्स (वैकल्पिक*)

4 x 470 ओम प्रतिरोधक

4 x 560 ओम प्रतिरोधक

4 x CC सात खंड प्रदर्शित करता है

4 x 3 मिमी एलईडी

4 एक्स एसपीडीटी स्पर्श स्विच

1 x 4 स्थिति सतह माउंट डीआईपी स्विच

२ x २५ गुणा २ या ४ x २५ शीर्षलेख

1x 2 बाय 5 पिन बॉक्स हेड

सोल्डरिंग आयरन

मिलाप

फ्लक्स

*(यदि इन प्रतिरोधों को छोड़ दिया जाता है तो संबंधित पिन के लिए आंतरिक पुलअप/पुलडाउन सक्षम होना चाहिए)

चरण 1: अपनी पसंद के पीसीबी निर्माता को Gerber अपलोड करें

अपने बोर्डों के लिए मैंने JLC PCB से ऑर्डर किया।

मैंने जो एकमात्र बदलाव किया वह वह रंग था जिसे मैं मोजो के काले रंग से मिलाना चाहता था।

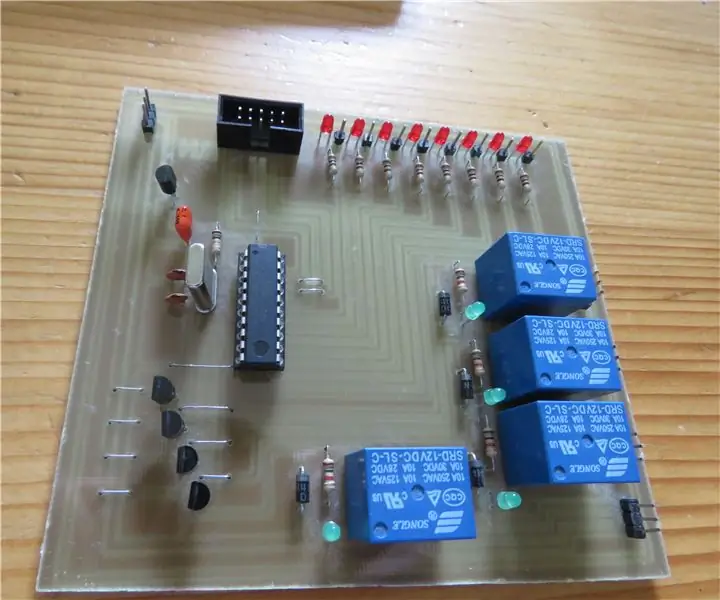

चरण 2: बोर्ड असेंबली

सोल्डरिंग करते समय मुझे हमेशा सबसे कम हिस्सों को पहले मिलाप करना उपयोगी लगता है इसलिए प्रतिरोधों से शुरू करना एक अच्छा विचार है।

R5, R6, R7, R8, R9, R10, R11 और R12 15k ओम प्रतिरोधक हैं जिनका उपयोग स्विच को नीचे खींचने के लिए किया जाता है (यदि आप आंतरिक पुलअप/पुलडाउन का उपयोग कर रहे हैं तो इसे अनदेखा करें)।

R1, R2, R3, R4 560 ओम रेसिस्टर्स हैं जो 7 सेगमेंट डिस्प्ले के माध्यम से करंट को सीमित करने के लिए जिम्मेदार हैं।

R13, R14, R15, R16 470 ओम प्रतिरोधक हैं जो 4 एलईडी के माध्यम से करंट को सीमित करने के लिए जिम्मेदार हैं।

अगला सोल्डर उस क्रम में डिप स्विच, टैक्टाइल स्विच, एलईडी, सात सेगमेंट डिस्प्ले और बॉक्स हेडर कनेक्टर को मिलाप करता है।

अब पिनों को संरेखित करने के लिए 25 को 2 (या 2 25 बाय 1) को मोजो में रखें। पिन के साथ ढाल को संरेखित करें और इसे जगह में मिलाप करें।

चरण 3: सॉफ्टवेयर सेटअप

सॉफ्टवेयर के लिए Alchitry वेबसाइट का जिक्र करने से आपको पता चल जाएगा कि आपको आरंभ करने और Xilinx ISE को स्थापित करने की क्या आवश्यकता है। हालाँकि.ucf फ़ाइल को बदलना ताकि यह जान सके कि आपके प्रोग्राम को चलाने के लिए कौन से पिन महत्वपूर्ण हैं।

यहाँ.ucf फ़ाइल है जिसका उपयोग मैं ढाल के साथ करता हूँ:

कॉन्फिग VCCAUX=3.3;

नेट "क्लक" TNM_NET = clk; TIMESPEC TS_clk = PERIOD "clk" ५० MHz उच्च ५०%; NET "clk" LOC = P56 | IOSTANDARD = LVTTL; NET "rst_n" LOC = P38 | IOSTANDARD = LVTTL; NET "cclk" LOC = P70 | IOSTANDARD = LVTTL; NET "spi_mosi" LOC = P44 | IOSTANDARD = LVTTL; NET "spi_miso" LOC = P45 | IOSTANDARD = LVTTL; NET "spi_ss" LOC = P48 | IOSTANDARD = LVTTL; NET "spi_sck" LOC = P43 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P46 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P61 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P62 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P65 | IOSTANDARD = LVTTL; नेट "avr_tx" एलओसी = P55 | IOSTANDARD = LVTTL; नेट "avr_rx" एलओसी = P59 | IOSTANDARD = LVTTL; NET "avr_rx_busy" LOC = P39 | IOSTANDARD = LVTTL; नेट "क्यू [0]" एलओसी = पी26 | IOSTANDARD = LVTTL; नेट "क्यू[1]" एलओसी = पी23 | IOSTANDARD = LVTTL; नेट "क्यू[2]" एलओसी = पी21 | IOSTANDARD = LVTTL; नेट "क्यू [3]" एलओसी = पी16 | IOSTANDARD = LVTTL; नेट "एस [0]" एलओसी = पी 7 | IOSTANDARD = LVTTL; नेट "एस [1]" एलओसी = पी 9 | IOSTANDARD = LVTTL; नेट "एस[2]" एलओसी = पी11 | IOSTANDARD = LVTTL; नेट "एस [3]" एलओसी = पी 14 | IOSTANDARD = LVTTL; नेट "पीबी [1]" एलओसी = पी 30 | IOSTANDARD = LVTTL; नेट "पीबी[2]" एलओसी = पी27 | IOSTANDARD = LVTTL; नेट "पीबी [3]" एलओसी = पी 24 | IOSTANDARD = LVTTL; नेट "पीबी [4]" एलओसी = पी 22 | IOSTANDARD = LVTTL; नेट "सेवा [0]" एलओसी = पी57 | IOSTANDARD = LVTTL; NET "sevsegb[0]" LOC = P58 | IOSTANDARD = LVTTL; NET "sevsegc[0]" LOC = P66 | IOSTANDARD = LVTTL; NET "sevsegd[0]" LOC = P67 | IOSTANDARD = LVTTL; नेट "सेवसेज [0]" एलओसी = पी74 | IOSTANDARD = LVTTL; NET "sevsegf[0]" LOC = P75 | IOSTANDARD = LVTTL; नेट "सेवसेग [0]" एलओसी = पी78 | IOSTANDARD = LVTTL; NET "sevsegdp[0]" LOC = P80 | IOSTANDARD = LVTTL; नेट "सेवेगा [1]" एलओसी = पी82 | IOSTANDARD = LVTTL; NET "sevsegb[1]" LOC = P83 | IOSTANDARD = LVTTL; NET "sevsegc[1]" LOC = P84 | IOSTANDARD = LVTTL; NET "sevsegd[1]" LOC = P85 | IOSTANDARD = LVTTL; नेट "सेवसेज[1]" एलओसी = पी87 | IOSTANDARD = LVTTL; NET "sevsegf[1]" LOC = P88 | IOSTANDARD = LVTTL; NET "sevsegg[1]" LOC = P92 | IOSTANDARD = LVTTL; NET "sevsegdp[1]" LOC = P94 | IOSTANDARD = LVTTL; नेट "सेवेगा [2]" एलओसी = पी97 | IOSTANDARD = LVTTL; NET "sevsegb[2]" LOC = P98 | IOSTANDARD = LVTTL; NET "sevsegc[2]" LOC = P99 | IOSTANDARD = LVTTL; NET "sevsegd[2]" LOC = P100 | IOSTANDARD = LVTTL; नेट "सेवसेज[2]" एलओसी = पी101 | IOSTANDARD = LVTTL; NET "sevsegf[2]" LOC = P102 | IOSTANDARD = LVTTL; नेट "सेवसेग[2]" एलओसी = पी104 | IOSTANDARD = LVTTL; NET "sevsegdp[2]" LOC = P111 | IOSTANDARD = LVTTL; नेट "सेवा [3]" एलओसी = पी११४ | IOSTANDARD = LVTTL; NET "sevsegb[3]" LOC = P115 | IOSTANDARD = LVTTL; NET "sevsegc[3]" LOC = P116 | IOSTANDARD = LVTTL; NET "sevsegd[3]" LOC = P117 | IOSTANDARD = LVTTL; NET "सेवसेज [3]" LOC = P118 | IOSTANDARD = LVTTL; NET "sevsegf[3]" LOC = P119 | IOSTANDARD = LVTTL; नेट "सेवसेग [3]" एलओसी = पी1120 | IOSTANDARD = LVTTL; NET "sevsegdp[3]" LOC = P121 | IOSTANDARD = LVTTL;

याद रखें कि यदि आपने.ucf में पिन को संपादित करने के लिए पुलडाउन रेसिस्टर्स को स्थापित नहीं किया है

| नीचे खींचना; हे

| अपने आप को रोकना;

यदि आप किसी भी चीज़ के लिए ब्लॉक का उपयोग करना चाहते हैं तो कनेक्शन इस प्रकार हैं। बायां ब्लॉक पिन नंबर है और दायां मोजो पिन नंबर है जिसे आपको अपने.ucf में असाइन करना चाहिए:

पिन 1 = 29

पिन 2 = 51

पिन 3 = 32

पिन 4 = 41

पिन 5 = 34

पिन 6 = 35

पिन 7 = 40

पिन 8 = 33

पिन 9 = जीएनडी

पिन 10 = +V

सिफारिश की:

ड्राइवमॉल बोर्ड का विकास: 5 कदम

ड्राइवमॉल बोर्ड का विकास: इस ट्यूटोरियल में हम एक कस्टम Arduino बोर्ड बनाने के लिए बुनियादी कदम देखेंगे। बोर्ड डिजाइन के लिए KiCad और बोर्ड के लिए फर्मवेयर बनाने और लोड करने के लिए Arduino IDE का उपयोग किया जाने वाला सॉफ़्टवेयर है

DIY ESP32 विकास बोर्ड - ESPer: 5 कदम (चित्रों के साथ)

DIY ESP32 डेवलपमेंट बोर्ड - ESPer: तो हाल ही में मैं बहुत सारे IoTs (इंटरनेट ऑफ थिंग्स) के बारे में पढ़ रहा था और मुझ पर विश्वास करें, मैं इंटरनेट से कनेक्ट करने की क्षमता वाले इन अद्भुत उपकरणों में से किसी एक का परीक्षण करने के लिए इंतजार नहीं कर सकता था, मैं और मेरे हाथ काम पर लग जाओ। सौभाग्य से अवसर एक

माइक्रोकंट्रोलर के साथ अपना खुद का विकास बोर्ड बनाएं: 3 चरण (चित्रों के साथ)

माइक्रोकंट्रोलर के साथ अपना खुद का विकास बोर्ड बनाएं: क्या आप कभी माइक्रोकंट्रोलर के साथ अपना खुद का विकास बोर्ड बनाना चाहते थे और आपको नहीं पता था कि कैसे। इस निर्देश में मैं आपको दिखाऊंगा कि इसे कैसे बनाया जाता है। आपको केवल इलेक्ट्रॉनिक्स, डिजाइनिंग सर्किट में ज्ञान की आवश्यकता है और प्रोग्रामिंग। यदि आपके पास कोई खोज है

एक माइक्रोकंट्रोलर विकास बोर्ड डिजाइन करना: 14 कदम (चित्रों के साथ)

एक माइक्रोकंट्रोलर डेवलपमेंट बोर्ड डिजाइन करना: क्या आप एक निर्माता, शौक़ीन या हैकर हैं जो परफ़बोर्ड प्रोजेक्ट्स, डीआईपी आईसी और होम मेड पीसीबी से बोर्ड हाउस द्वारा निर्मित मल्टीलेयर पीसीबी और बड़े पैमाने पर उत्पादन के लिए तैयार एसएमडी पैकेजिंग से आगे बढ़ने में रुचि रखते हैं? तब यह शिक्षाप्रद आपके लिए है! यह गुई

AVR विकास बोर्ड: 3 कदम

AVR विकास बोर्ड: इंटरनेट Arduino के साथ परियोजनाओं से भरा है। कुछ समय के लिए सभी Arduino डेटा में ATMEGA328 माइक्रोकंट्रोलर के बारे में जानकारी गायब है। यह इंस्ट्रक्टेबल एवीआर माइक्रोकॉन्ट का उपयोग करके परियोजनाओं को कैसे विकसित किया जाए, इसकी शुरुआत को फिर से शुरू करना चाहता है