विषयसूची:

- चरण 1: Digilent's Zybo DMA ऑडियो डेमो प्राप्त करें

- चरण 2: विवाडो में कुछ बदलाव करें

- चरण 3: फ्रीआरटीओएस चालू करें

- चरण 4: लेजर हार्प कोड जोड़ें

- चरण 5: कोड के बारे में

- चरण 6: सेंसर को तार देना

- चरण 7: कंकाल का निर्माण

- चरण 8: लकड़ी के बाहरी हिस्से का निर्माण

- चरण 9: सभी टुकड़ों को एक साथ रखना

- चरण 10: रॉक आउट

वीडियो: Zybo बोर्ड पर लेजर हार्प सिंथेसाइज़र: 10 कदम (चित्रों के साथ)

2024 लेखक: John Day | [email protected]. अंतिम बार संशोधित: 2024-01-30 09:23

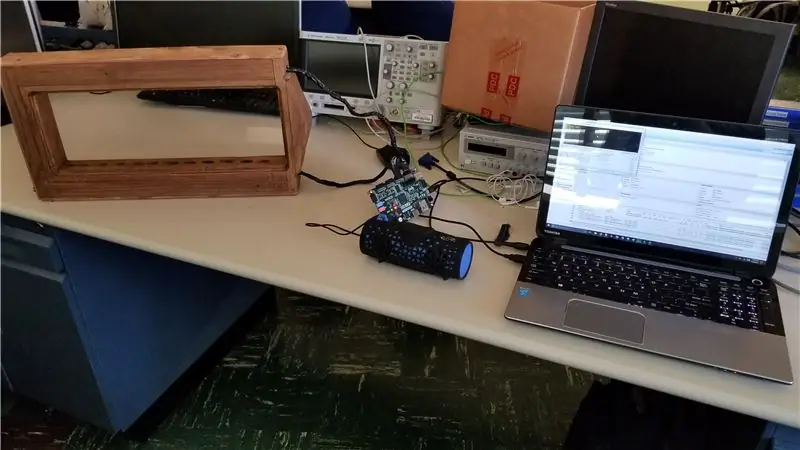

इस ट्यूटोरियल में हम एक सीरियल इंटरफ़ेस के साथ IR सेंसर का उपयोग करके पूरी तरह कार्यात्मक लेजर वीणा बनाएंगे जो उपयोगकर्ता को उपकरण की ट्यूनिंग और टोन को बदलने की अनुमति देगा। यह वीणा पुराने वाद्य यंत्र की 21वीं सदी की रीमेक होगी। सिस्टम को विवाडो डिज़ाइन सूट के साथ Xilinx Zybo डेवलपमेंट बोर्ड का उपयोग करके बनाया गया था। परियोजना को पूरा करने के लिए आपको क्या चाहिए:

- 12 आईआर सेंसर और एमिटर (स्ट्रिंग्स की संख्या के आधार पर कम या ज्यादा इस्तेमाल किया जा सकता है)

- Zybo Zynq-7000 विकास बोर्ड

- मुफ्त आरटीओएस

- विवाडो डिजाइन सूट

- तार (सेंसर को बोर्ड से जोड़ने के लिए)

- पीवीसी पाइप के ३ टुकड़े ((२) १८ इंच और (१) ८ इंच)

- 2 पीवीसी कोहनी

चरण 1: Digilent's Zybo DMA ऑडियो डेमो प्राप्त करें

इस परियोजना का FPGA पक्ष काफी हद तक यहां मिले डेमो प्रोजेक्ट पर आधारित है। यह मेमोरी से सीधे डेटा भेजने के लिए डायरेक्ट मेमोरी एक्सेस का उपयोग करता है जिसे प्रोसेसर I2S ऑडियो ब्लॉक में AXI स्ट्रीम पर लिख सकता है। निम्नलिखित कदम आपको डीएमए ऑडियो डेमो प्रोजेक्ट को ऊपर और चलाने में मदद करेंगे:

- Zybo बोर्ड के लिए बोर्ड फ़ाइल का एक नया संस्करण आवश्यक हो सकता है। विवाडो के लिए नई बोर्ड फाइलें प्राप्त करने के लिए इन निर्देशों का पालन करें।

- विवाडो में डेमो प्रोजेक्ट खोलने के लिए इस पेज पर दिए गए निर्देशों में चरण 1 और 2 का पालन करें। विवाडो पद्धति का उपयोग करें, एसडीके हार्डवेयर हैंडऑफ़ का नहीं।

- आपको एक संदेश मिल सकता है जो कहता है कि आपके कुछ आईपी ब्लॉक अपडेट किए जाने चाहिए। यदि ऐसा है, तो "आईपी स्थिति दिखाएं" चुनें और फिर आईपी स्थिति टैब में सभी पुराने आईपी का चयन करें और "चयनित अपग्रेड करें" पर क्लिक करें। जब यह समाप्त हो जाता है और एक विंडो पॉप अप करके पूछती है कि क्या आप आउटपुट उत्पाद उत्पन्न करना चाहते हैं, तो आगे बढ़ें और "जेनरेट करें" पर क्लिक करें। यदि आपको एक महत्वपूर्ण चेतावनी संदेश मिलता है, तो उसे अनदेखा करें।

- स्रोत फ़ाइलों को देखने के लिए विवाडो में डिज़ाइन से स्रोत टैब पर स्विच करें। ब्लॉक डिज़ाइन "डिज़ाइन_1" पर राइट-क्लिक करें और "एचडीएल रैपर बनाएं" चुनें। जब संकेत दिया जाए तो "उपयोगकर्ता संपादन की अनुमति देने के लिए कॉपी जेनरेट किए गए रैपर" का चयन करें। प्रोजेक्ट के लिए एक रैपर फ़ाइल जेनरेट की जाएगी।

- अब जबकि वे महत्वपूर्ण चरण जो किसी तरह अन्य ट्यूटोरियल में छूट गए थे, पूरे हो गए हैं, आप पहले से लिंक किए गए ट्यूटोरियल पर वापस लौट सकते हैं और चरण 4 से अंत तक जारी रख सकते हैं और सुनिश्चित कर सकते हैं कि डेमो प्रोजेक्ट सही ढंग से चलता है। यदि आपके पास इसे रिकॉर्ड करने के लिए ऑडियो इनपुट करने का कोई तरीका नहीं है, तो बस अपने हेडफ़ोन के साथ रिकॉर्ड करें और प्लेबैक बटन दबाने पर 5-10 सेकंड की फ़ज़ी ध्वनि सुनें। जब तक आप प्लेबैक बटन दबाते हैं, तब तक हेडफोन जैक से कुछ निकलता है, यह शायद सही ढंग से काम कर रहा है।

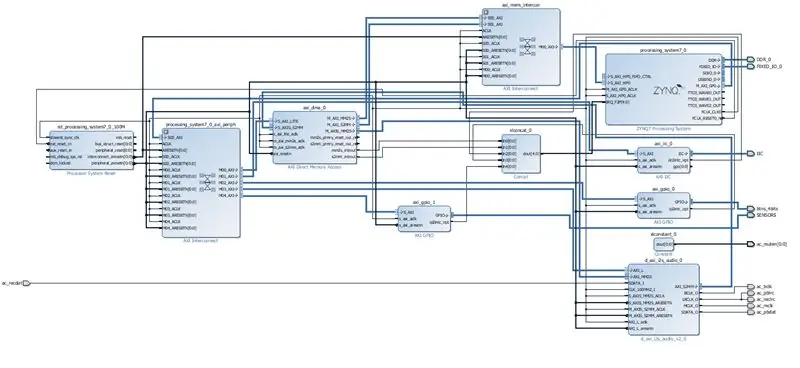

चरण 2: विवाडो में कुछ बदलाव करें

तो अब आपके पास Digilent का DMA ऑडियो डेमो काम कर रहा है, लेकिन वह यहां अंतिम लक्ष्य नहीं है। इसलिए हमें विवाडो में वापस जाना होगा और कुछ बदलाव करने होंगे ताकि हमारे सेंसर को पीएमओडी हेडर में प्लग किया जा सके और हम सॉफ्टवेयर के पक्ष में उनके मूल्य का उपयोग कर सकें।

- विवाडो में ब्लॉक आरेख खोलें

- ब्लॉक आरेख में खाली जगह पर राइट-क्लिक करके और मेनू से "आईपी जोड़ें" का चयन करके एक GPIO ब्लॉक बनाएं। "AXI GPIO" ढूंढें और चुनें।

- नए आईपी ब्लॉक पर डबल क्लिक करें और आईपी विंडो को फिर से कस्टमाइज़ करने के लिए आईपी कॉन्फ़िगरेशन टैब पर जाएं। सभी इनपुट का चयन करें और चौड़ाई को बारह पर सेट करें, क्योंकि हमारे वीणा पर 12 "स्ट्रिंग्स" होंगे और इसलिए 12 सेंसर की आवश्यकता होगी। यदि आप कम या अधिक सेंसर का उपयोग करना चाहते हैं तो इस संख्या को उचित रूप से समायोजित करें। इंटरप्ट सक्षम भी सेट करें।

- नए GPIO IP ब्लॉक पर राइट क्लिक करें और "रन कनेक्शन ऑटोमेशन" चुनें। AXI बॉक्स को चेक करें और ओके पर हिट करें। यह AXI इंटरफ़ेस को स्वचालित रूप से कनेक्ट करना चाहिए, लेकिन ब्लॉक के आउटपुट को असंबद्ध छोड़ देना चाहिए।

- अतिरिक्त व्यवधान के लिए जगह बनाने के लिए, xlconcat_0 IP ब्लॉक पर डबल क्लिक करें और पोर्ट की संख्या 4 से 5 में बदलें। फिर आप ip2intc_irpt पिन को नए GPIO ब्लॉक से xlconcat ब्लॉक पर नए अप्रयुक्त पोर्ट से कनेक्ट कर सकते हैं।

- नए GPIO IP ब्लॉक के "GPIO" आउटपुट पर राइट क्लिक करें और "बाहरी बनाएं" चुनें। पता लगाएँ कि रेखा कहाँ जाती है और छोटे बग़ल में पेंटागन पर क्लिक करें और बाईं ओर एक विंडो खुलनी चाहिए जहाँ आप नाम बदल सकते हैं। नाम बदलकर "सेंसर" कर दें। उसी नाम का उपयोग करना महत्वपूर्ण है यदि आप चाहते हैं कि हमारे द्वारा प्रदान की जाने वाली बाधा फ़ाइल काम करे, अन्यथा आपको बाधाओं फ़ाइल में नाम बदलना होगा।

- स्रोत टैब में वापस, बाधा फ़ाइल ढूंढें और इसे हमारे द्वारा प्रदान की गई फ़ाइल से बदलें। आप या तो फ़ाइल को बदलने का विकल्प चुन सकते हैं या बस हमारी बाधाओं की फ़ाइल की सामग्री को कॉपी कर सकते हैं और इसे पुराने की सामग्री पर पेस्ट कर सकते हैं। हमारी बाधाओं में से एक महत्वपूर्ण चीज है जो पीएमओडी हेडर पर पुलअप रेसिस्टर्स को सक्षम करती है। यह हमारे द्वारा उपयोग किए जाने वाले विशेष सेंसर के लिए आवश्यक है, हालांकि सभी सेंसर समान नहीं हैं। यदि आपके सेंसर को पुलडाउन रेसिस्टर्स की आवश्यकता है तो आप "set_property PULLUP true" के हर इंस्टेंस को "set_property PULLDOWN true" से बदल सकते हैं। यदि उन्हें बोर्ड पर एक से भिन्न प्रतिरोधक मान की आवश्यकता है, तो आप इन पंक्तियों को हटा सकते हैं और बाहरी प्रतिरोधों का उपयोग कर सकते हैं। पिन नाम बाधाओं फ़ाइल में टिप्पणियों में हैं, और वे Zybo Schematics में पहले आरेख में लेबल के अनुरूप हैं। पृष्ठ जो यहां पाया जा सकता है। यदि आप अलग-अलग पीएमओडी पिन का उपयोग करना चाहते हैं तो बस बाधा फ़ाइल में नामों को योजनाबद्ध में लेबल से मिलाएं। हम पीएमओडी हेडर जेई और जेडी का उपयोग करते हैं, और प्रत्येक पर छह डेटा पिन का उपयोग करते हैं, पिन 1 और 7 को छोड़ देते हैं। आपके सेंसर को जोड़ते समय यह जानकारी महत्वपूर्ण है। जैसा कि योजनाबद्ध में दिखाया गया है, पीएमओडीएस पर पिन 6 और 12 वीसीसी हैं और पिन 5 और 11 ग्राउंड हैं।

- एचडीएल रैपर को पहले की तरह फिर से जनरेट करें और पुराने वाले को कॉपी और ओवरराइट करें। जब यह हो जाए, तो बिटस्ट्रीम उत्पन्न करें और पहले की तरह हार्डवेयर निर्यात करें, और एसडीके को फिर से लॉन्च करें। यदि आपसे पूछा जाए कि क्या आप पुरानी हार्डवेयर फ़ाइल को बदलना चाहते हैं, तो इसका उत्तर हां है। जब आप हार्डवेयर निर्यात करते हैं तो एसडीके को बंद करना शायद सबसे अच्छा होता है ताकि इसे ठीक से बदल दिया जा सके।

- एसडीके लॉन्च करें।

चरण 3: फ्रीआरटीओएस चालू करें

अगला कदम ज़ीबो बोर्ड पर फ्रीआरटीओएस चलाना है।

- यदि आपके पास पहले से एक प्रति नहीं है, तो यहां फ्रीआरटीओएस डाउनलोड करें और फाइलें निकालें।

- FreeRTOSv9.0.0\FreeRTOS\Demo\CORTEX_A9_Zynq_ZC702\RTOSDemo पर स्थित FreeRTOS Zynq डेमो आयात करें। आयात प्रक्रिया काफी हद तक अन्य डेमो प्रोजेक्ट के समान ही है, हालांकि फ्रीआरटीओएस ज़िनक डेमो फ्रीआरटीओएस फ़ोल्डर में अन्य फाइलों पर निर्भर करता है, इसलिए आपको फाइलों को अपने कार्यक्षेत्र में कॉपी नहीं करना चाहिए। इसके बजाय, आपको पूरे फ्रीआरटीओएस फ़ोल्डर को अपने प्रोजेक्ट फ़ोल्डर के अंदर रखना चाहिए।

- "फाइल" -> "नया" -> "बोर्ड सपोर्ट पैकेज" पर जाकर एक नया बोर्ड सपोर्ट पैकेज बनाएं। सुनिश्चित करें कि स्टैंडअलोन चयनित है और समाप्त पर क्लिक करें। एक पल के बाद एक विंडो पॉप अप होगी, lwip141 के बगल में स्थित बॉक्स को चेक करें (यह फ्रीआरटीओएस डेमो में से एक को संकलित करने में विफल होने से रोकता है) और ओके को हिट करें। उसके बाद RTOSdemo प्रोजेक्ट पर राइट क्लिक करें और "प्रॉपर्टीज" पर जाएं, "प्रोजेक्ट रेफरेंस" टैब पर जाएं, और आपके द्वारा बनाए गए नए bsp के बगल में स्थित बॉक्स को चेक करें। उम्मीद है कि इसे पहचाना जाएगा लेकिन कभी-कभी Xilinx SDK इस तरह की चीज़ के बारे में अजीब हो सकता है। यदि आपको इस चरण के बाद भी कोई त्रुटि मिलती है कि xparameters.h गुम है या ऐसा कुछ है तो इस चरण को दोहराने का प्रयास करें और शायद SDK से बाहर निकलकर पुन: लॉन्च करें।

चरण 4: लेजर हार्प कोड जोड़ें

अब जब फ्रीआरटीओएस आयात हो गया है, तो आप लेजर वीणा परियोजना से फाइलों को फ्रीआरटीओएस डेमो में ला सकते हैं

- FreeRTOS डेमो में src फोल्डर के तहत एक नया फोल्डर बनाएं और इस फोल्डर में main.c को छोड़कर सभी प्रदान की गई c फाइलों को कॉपी और पेस्ट करें।

- RTOSDemo main.c को दिए गए main.c से बदलें।

- यदि सब कुछ सही ढंग से किया जाता है, तो आपको इस बिंदु पर लेजर वीणा कोड चलाने में सक्षम होना चाहिए। परीक्षण उद्देश्यों के लिए, डीएमए डेमो प्रोजेक्ट में इस्तेमाल किया गया बटन इनपुट अब बिना सेंसर के ध्वनि चलाने के लिए उपयोग किया जाता है (चार मुख्य बटनों में से कोई भी काम करेगा)। हर बार जब आप इसे दबाते हैं तो यह एक स्ट्रिंग बजाएगा और सिस्टम में सभी स्ट्रिंग्स के माध्यम से कई प्रेस पर चक्र करेगा। Zybo बोर्ड पर हेडफ़ोन जैक में कुछ हेडफ़ोन या स्पीकर प्लग करें और सुनिश्चित करें कि जब आप एक बटन दबाते हैं तो आप स्ट्रिंग्स की आवाज़ सुन सकते हैं।

चरण 5: कोड के बारे में

आप में से कई लोग जो इस ट्यूटोरियल को पढ़ रहे हैं, शायद यहां ऑडियो सेट अप करना या कुछ अलग करने के लिए डीएमए का उपयोग करना, या एक अलग संगीत वाद्ययंत्र बनाना सीखना है। इसी कारण से अगले कुछ खंड यह वर्णन करने के लिए समर्पित हैं कि डीएमए का उपयोग करके एक कार्यशील ऑडियो आउटपुट प्राप्त करने के लिए पहले वर्णित हार्डवेयर के साथ प्रदान किया गया कोड कैसे काम करता है। यदि आप समझते हैं कि कोड के टुकड़े क्यों हैं तो आप उन्हें जो कुछ भी बनाना चाहते हैं, उसके लिए उन्हें समायोजित करने में सक्षम होना चाहिए।

बीच में आता है

पहले मैं उल्लेख करूँगा कि इस परियोजना में व्यवधान कैसे उत्पन्न होते हैं। जिस तरह से हमने इसे पहले एक इंटरप्ट वेक्टर टेबल स्ट्रक्चर बनाकर किया था जो आईडी, इंटरप्ट हैंडलर और प्रत्येक इंटरप्ट के लिए डिवाइस का संदर्भ रखता है। इंटरप्ट आईडी xparameters.h से आते हैं। इंटरप्ट हैंडलर एक फ़ंक्शन है जिसे हमने डीएमए और जीपीआईओ के लिए लिखा है, और I2C इंटरप्ट Xlic I2C ड्राइवर से आता है। डिवाइस संदर्भ प्रत्येक डिवाइस के उदाहरणों को इंगित करता है जिसे हम कहीं और प्रारंभ करते हैं। _init_audio फ़ंक्शन के अंत के पास एक लूप इंटरप्ट वेक्टर तालिका में प्रत्येक आइटम के माध्यम से जाता है और इंटरप्ट को जोड़ने और सक्षम करने के लिए दो फ़ंक्शन, XScuGic_Connect() और XScuGic_Enable() को कॉल करता है। वे xInterruptController का संदर्भ देते हैं, जो कि डिफ़ॉल्ट रूप से FreeRTOS main.c में बनाया गया एक इंटरप्ट कंट्रोलर है। इसलिए मूल रूप से हम अपने प्रत्येक इंटरप्ट को इस इंटरप्ट कंट्रोलर से जोड़ते हैं जो पहले से ही हमारे लिए फ्रीआरटीओएस द्वारा बनाया गया था।

डीएमए

डीएमए इनिशियलाइज़ेशन कोड lh_main.c में शुरू होता है। सबसे पहले XAxiDma संरचना का एक स्थिर उदाहरण घोषित किया जाता है। फिर _init_audio() फ़ंक्शन में यह कॉन्फ़िगर हो जाता है। सबसे पहले डेमो प्रोजेक्ट से कॉन्फ़िगर फ़ंक्शन को कॉल किया जाता है, जो dma.c में है। यह बहुत अच्छी तरह से प्रलेखित है और सीधे डेमो से आता है। फिर इंटरप्ट कनेक्ट और सक्षम हो जाता है। इस प्रोजेक्ट के लिए केवल मास्टर-टू-स्लेव इंटरप्ट की आवश्यकता है, क्योंकि सभी डेटा डीएमए द्वारा I2S कंट्रोलर को भेजा जा रहा है। यदि आप ऑडियो रिकॉर्ड करना चाहते हैं, तो आपको स्लेव-टू-मास्टर इंटरप्ट की भी आवश्यकता होगी। मास्टर-टू-स्लेव इंटरप्ट को तब बुलाया जाता है जब डीएमए आपके द्वारा भेजे जाने वाले डेटा को भेजने के लिए समाप्त कर देता है। यह रुकावट हमारी परियोजना के लिए अविश्वसनीय रूप से महत्वपूर्ण है क्योंकि हर बार जब डीएमए ऑडियो नमूनों का एक बफर भेजना समाप्त करता है तो उसे तुरंत अगले बफर को भेजना शुरू कर देना चाहिए, अन्यथा भेजने के बीच एक श्रव्य देरी होगी। dma_mm2s_ISR() फ़ंक्शन के अंदर आप देख सकते हैं कि हम इंटरप्ट को कैसे संभालते हैं। महत्वपूर्ण हिस्सा अंत के पास है जहां हम _audio_task() को सूचित करने के लिए xSemaphoreGiveFromISR() और portYIELD_FROM_ISR() का उपयोग करते हैं कि यह अगला डीएमए हस्तांतरण शुरू कर सकता है। जिस तरह से हम लगातार ऑडियो डेटा भेजते हैं वह दो बफ़र्स के बीच बारी-बारी से होता है। जब एक बफर को I2C ब्लॉक में प्रेषित किया जा रहा है, तो दूसरा बफर इसके मूल्यों की गणना और संग्रहीत कर रहा है। फिर जब डीएमए से रुकावट आती है तो सक्रिय बफर स्विच हो जाता है और हाल ही में लिखे गए बफर को स्थानांतरित करना शुरू हो जाता है जबकि पहले से स्थानांतरित बफर नए डेटा के साथ अधिलेखित होने लगता है। _audio_task फ़ंक्शन का मुख्य भाग वह है जहाँ fnAudioPlay() को कॉल किया जाता है। fnAudioPlay () डीएमए इंस्टेंस, बफर की लंबाई और बफर के लिए एक पॉइंटर लेता है जिससे डेटा स्थानांतरित किया जाएगा। I2S रजिस्टरों को कुछ मान भेजे जाते हैं ताकि यह पता चल सके कि अधिक नमूने आ रहे हैं। फिर ट्रांसफर शुरू करने के लिए XAxiDma_SimpleTransfer() को कॉल किया जाता है।

I2S ऑडियो

audio.c और audio.h वे हैं जहां I2S इनिशियलाइज़ेशन होता है। I2S इनिशियलाइज़ेशन कोड कोड का एक बहुत ही सामान्य हिस्सा है जो कई जगहों पर तैर रहा है, आपको अन्य स्रोतों से थोड़ी भिन्नता मिल सकती है लेकिन यह काम करना चाहिए। यह बहुत अच्छी तरह से प्रलेखित है और वीणा परियोजना के लिए इसे बदलने की ज्यादा जरूरत नहीं है। डीएमए ऑडियो डेमो, जिससे यह आया है, में माइक या लाइन इनपुट पर स्विच करने के लिए कार्य हैं ताकि यदि आपको उस कार्यक्षमता की आवश्यकता हो तो आप उनका उपयोग कर सकें।

ध्वनि संश्लेषण

यह वर्णन करने के लिए कि ध्वनि संश्लेषण कैसे काम करता है, मैं विकास में उपयोग किए जाने वाले प्रत्येक ध्वनि मॉडल को सूचीबद्ध करने जा रहा हूं जो अंतिम विधि का नेतृत्व करता है, क्योंकि यह आपको यह समझ देगा कि इसे जिस तरह से किया जाता है उसे क्यों किया जाता है।

विधि 1: प्रत्येक स्ट्रिंग के लिए उस स्ट्रिंग के संगीत नोट के लिए संगत आवृत्ति पर साइन मानों की एक अवधि की गणना की जाती है और एक सरणी में संग्रहीत किया जाता है। उदाहरण के लिए, सरणी की लंबाई नमूनों में साइन लहर की अवधि होगी, जो नमूनों / चक्र के # के बराबर होती है। यदि नमूनाकरण दर ४८kHz है और नोट आवृत्ति १०० हर्ट्ज है, तो ४८,००० नमूने/सेकंड और १०० चक्र/सेकंड हैं जो प्रति चक्र ४८०० नमूनों के लिए अग्रणी हैं, और सरणी की लंबाई ४८०० नमूने होगी और इसमें एक पूर्ण के मान शामिल होंगे साइन लहर अवधि। जब स्ट्रिंग बजाई जाती है, तो ऑडियो सैंपल बफर को साइन वेव एरे से एक वैल्यू लेकर और सैंपल के रूप में ऑडियो बफर में डालकर भर दिया जाता है, फिर इंडेक्स को साइन वेव ऐरे में बढ़ा दिया जाता है ताकि कोर्स पर हमारे पिछले उदाहरण का उपयोग किया जा सके। 4800 नमूनों में से एक साइन तरंग चक्र ऑडियो बफर में डाला जाता है। सरणी अनुक्रमणिका पर एक मॉड्यूलो ऑपरेशन का उपयोग किया जाता है ताकि यह हमेशा 0 और लंबाई के बीच हो, और जब सरणी अनुक्रमणिका एक निश्चित सीमा से अधिक हो जाती है (जैसे शायद 2 सेकंड के नमूने के लायक) स्ट्रिंग बंद हो जाती है। एक ही समय में कई स्ट्रिंग्स चलाने के लिए, प्रत्येक स्ट्रिंग्स के ऐरे इंडेक्स को अलग से ट्रैक करें और प्रत्येक सैंपल प्राप्त करने के लिए प्रत्येक स्ट्रिंग्स की साइन वेव से मान को एक साथ जोड़ें।

विधि 2: अधिक संगीतमय स्वर बनाने के लिए, हम पिछले मॉडल से शुरू करते हैं और प्रत्येक मौलिक आवृत्ति में हार्मोनिक्स जोड़ते हैं। हार्मोनिक फ़्रीक्वेंसी वे फ़्रीक्वेंसी हैं जो मौलिक फ़्रीक्वेंसी के पूर्णांक गुणक हैं। इसके विपरीत जब दो असंबंधित आवृत्तियों को एक साथ जोड़ दिया जाता है, जिसके परिणामस्वरूप दो अलग-अलग ध्वनियाँ एक साथ बजती हैं, जब हार्मोनिक्स को एक साथ जोड़ा जाता है तो यह सिर्फ एक ध्वनि की तरह बजती रहती है, लेकिन एक अलग स्वर के साथ। इसे पूरा करने के लिए, हर बार जब हम ऑडियो नमूने में स्थान (सरणी अनुक्रमणिका% सरणी लंबाई) पर साइन तरंग का मान जोड़ते हैं, तो हम (2 * सरणी अनुक्रमणिका% सरणी लंबाई), और (3 * सरणी अनुक्रमणिका% सरणी लंबाई) भी जोड़ते हैं), और इसी तरह कई हार्मोनिक्स वांछित हैं। ये गुणा किए गए सूचकांक साइन लहर को उन आवृत्तियों पर पार करेंगे जो मूल आवृत्ति के पूर्णांक गुणक हैं। स्वर के अधिक नियंत्रण की अनुमति देने के लिए, प्रत्येक हार्मोनिक के मूल्यों को एक चर से गुणा किया जाता है जो समग्र ध्वनि में उस हार्मोनिक की मात्रा का प्रतिनिधित्व करता है। उदाहरण के लिए, मौलिक साइन वेव में इसके मूल्यों को 6 से गुणा किया जा सकता है ताकि इसे समग्र ध्वनि में अधिक कारक बनाया जा सके, जबकि 5 वें हार्मोनिक में 1 का गुणक हो सकता है, जिसका अर्थ है कि इसके मान समग्र ध्वनि में बहुत कम योगदान करते हैं।

विधि 3: ठीक है, तो अब हमारे पास नोट्स पर बहुत अच्छा स्वर है, लेकिन अभी भी एक बहुत ही महत्वपूर्ण समस्या है: वे एक निश्चित अवधि के लिए एक निश्चित मात्रा में खेलते हैं। एक वास्तविक वाद्य यंत्र की तरह ध्वनि करने के लिए बजाए जाने वाले तार का आयतन समय के साथ सुचारू रूप से क्षय होना चाहिए। इसे पूरा करने के लिए, एक सरणी एक घातीय रूप से क्षय होने वाले फ़ंक्शन के मानों से भर जाती है। अब जब ऑडियो नमूने बनाए जा रहे हैं, तो प्रत्येक स्ट्रिंग से आने वाली ध्वनि की गणना पिछली विधि की तरह की जाती है, लेकिन इससे पहले कि इसे ऑडियो नमूने में जोड़ा जाता है, यह घातीय क्षय फ़ंक्शन सरणी में उस स्ट्रिंग्स एरे इंडेक्स के मान से गुणा हो जाता है। यह समय के साथ ध्वनि को सुचारू रूप से समाप्त कर देता है। जब सरणी अनुक्रमणिका क्षय सरणी के अंत तक पहुँचती है, तो स्ट्रिंग रोक दी जाती है।

विधि 4: यह अंतिम चरण वह है जो वास्तव में स्ट्रिंग को उनकी यथार्थवादी स्ट्रिंग ध्वनि देता है। इससे पहले कि वे सुखद लग रहे थे लेकिन स्पष्ट रूप से संश्लेषित। वास्तविक दुनिया की वीणा स्ट्रिंग का बेहतर अनुकरण करने की कोशिश करने के लिए, प्रत्येक हार्मोनिक को एक अलग क्षय दर सौंपी जाती है। वास्तविक स्ट्रिंग्स में, जब स्ट्रिंग को पहली बार मारा जाता है, तो उच्च आवृत्ति वाले हार्मोनिक्स की एक उच्च सामग्री होती है जो उस प्रकार की प्लकिंग ध्वनि पैदा करती है जिसकी हम एक स्ट्रिंग से अपेक्षा करते हैं। ये उच्च आवृत्ति वाले हार्मोनिक्स बहुत संक्षेप में ध्वनि का मुख्य भाग होते हैं, स्ट्रिंग की ध्वनि को मारा जाता है, लेकिन धीमी हार्मोनिक्स के रूप में वे बहुत जल्दी क्षय हो जाते हैं। ध्वनि संश्लेषण में उपयोग किए जाने वाले प्रत्येक हार्मोनिक संख्या के लिए एक क्षय सरणी बनाई जाती है, प्रत्येक की अपनी क्षय दर होती है। अब प्रत्येक हार्मोनिक को स्वतंत्र रूप से स्ट्रिंग के सरणी सूचकांक पर इसके संबंधित क्षय सरणी के मूल्य से गुणा किया जा सकता है और ध्वनि में जोड़ा जा सकता है।

कुल मिलाकर ध्वनि संश्लेषण सहज है लेकिन गणना भारी है। एक बार में पूरी स्ट्रिंग ध्वनि को स्मृति में संग्रहीत करने में बहुत अधिक मेमोरी लगेगी, लेकिन प्रत्येक फ्रेम के बीच साइन तरंग और घातांक फ़ंक्शन की गणना करने में ऑडियो प्लेबैक की दर को बनाए रखने में बहुत लंबा समय लगेगा। गणना में तेजी लाने के लिए कोड में कई तरकीबों का उपयोग किया जाता है। साइन और घातीय क्षय सारणी के प्रारंभिक निर्माण को छोड़कर सभी गणित पूर्णांक प्रारूप में किए जाते हैं, जिसके लिए 24 बिट ऑडियो आउटपुट में उपलब्ध संख्यात्मक स्थान को फैलाने की आवश्यकता होती है। उदाहरण के लिए, साइन टेबल 150 के आयाम का है ताकि यह चिकना हो लेकिन इतना बड़ा नहीं कि एक साथ बजाए जाने वाले कई तार 24 बिट से अधिक हो सकें। इसी तरह, घातांक तालिका मानों को पूर्णांक में गोल करने और संग्रहीत करने से पहले 80 से गुणा किया जाता है। हार्मोनिक भार 0 और 10 के बीच असतत मान ले सकते हैं। साथ ही सभी नमूने वास्तव में दोगुने होते हैं और साइन तरंगों को 2 के द्वारा अनुक्रमित किया जाता है, प्रभावी रूप से नमूना दर को आधा कर देता है। यह अधिकतम आवृत्ति को सीमित करता है जिसे खेला जा सकता है, लेकिन स्ट्रिंग्स और हार्मोनिक्स की वर्तमान संख्या की गणना करने के लिए आवश्यक था ताकि जल्दी से पर्याप्त गणना की जा सके।

इस ध्वनि मॉडल को बनाने और इसे काम करने के लिए प्रोसेसर पक्ष पर काफी प्रयास किया गया था, और इस परियोजना के समय सीमा में इसे fpga पक्ष पर खरोंच से काम करना अविश्वसनीय रूप से कठिन होगा (कल्पना करें कि बिटस्ट्रीम को फिर से बनाना होगा हर समय ध्वनि का परीक्षण करने के लिए वेरिलॉग का एक टुकड़ा बदल दिया गया था)। हालांकि, इसे fpga पर करना संभवतः इसे करने का एक बेहतर तरीका हो सकता है, संभवतः नमूनों की जल्दी से गणना करने में सक्षम नहीं होने के मुद्दे को समाप्त करना और अधिक स्ट्रिंग्स, हार्मोनिक्स, और यहां तक कि ऑडियो प्रभाव या अन्य कार्यों को चलाने की अनुमति देना। प्रोसेसर पक्ष।

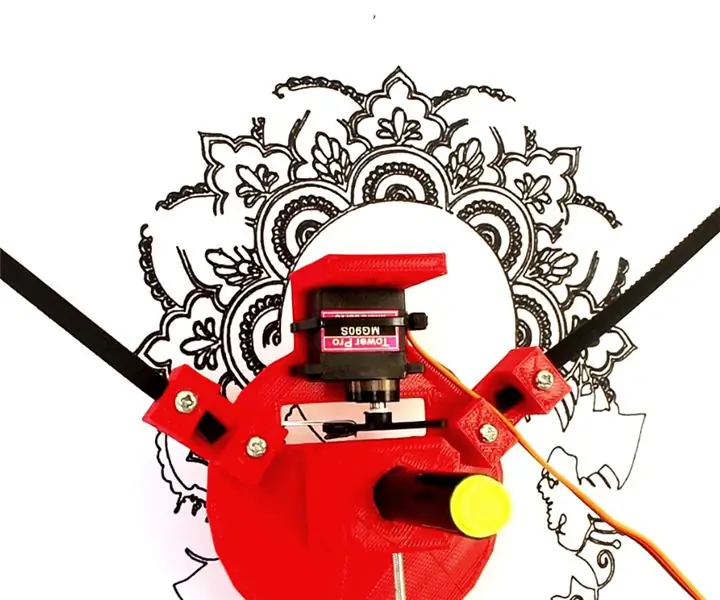

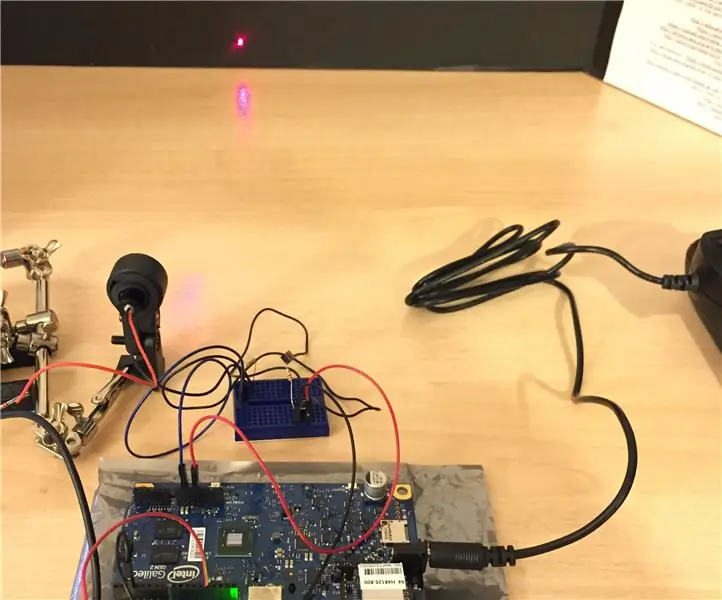

चरण 6: सेंसर को तार देना

स्ट्रिंग्स बनाने के लिए हमने IR ब्रेक बीम सेंसर का इस्तेमाल किया जो यह पता लगाएंगे कि स्ट्रिंग कब बजाई जा रही है। हमने निम्नलिखित लिंक से अपने सेंसर मंगवाए। सेंसर में पावर, ग्राउंड और डेटा वायर होता है जबकि एमिटर में केवल पावर और ग्राउंड वायर होता है। हमने एमिटर और सेंसर दोनों को पावर देने के लिए पीएमओडी हेडर से 3.3 वी और ग्राउंड पिन का इस्तेमाल किया। सभी सेंसर और एमिटर को पावर देने के लिए सभी सेंसर और एमिटर को समानांतर में जोड़ना आवश्यक है। सेंसर से डेटा तारों को प्रत्येक को अपने स्वयं के पीएमओडी पिन पर जाने की आवश्यकता होगी।

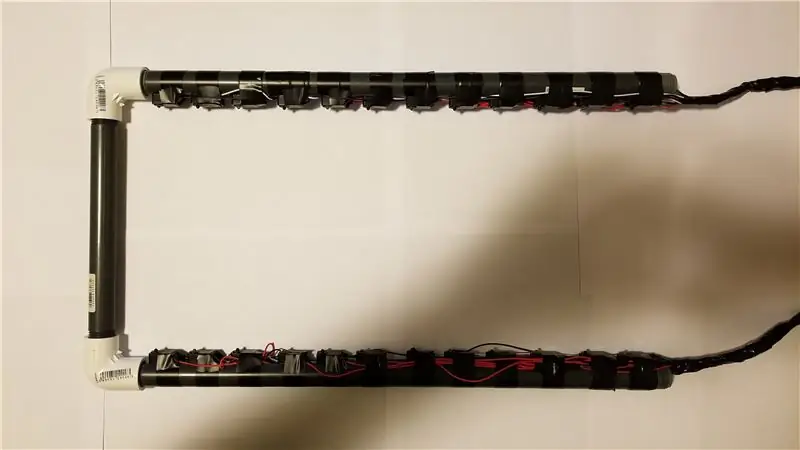

चरण 7: कंकाल का निर्माण

वीणा के आकार को बनाने के लिए सेंसर और उत्सर्जक को रखने के लिए तीन टुकड़ों को कंकाल के रूप में उपयोग किया जाता है। पीवीसी पाइप के दो 18 इंच के टुकड़ों में से एक पर सेंसर और उत्सर्जक को एक दूसरे से 1.5 इंच के क्रम में बारी-बारी से संरेखित करें और फिर उन्हें पाइप से नीचे टेप करें। अन्य 18 इंच के पीवीसी पाइप पर सेंसर और एमिटर को बारी-बारी से संरेखित करें, लेकिन ऑर्डर को ऑफसेट करना सुनिश्चित करें (यानी अगर पहले पाइप में पहले सेंसर था तो दूसरे में पहले एमिटर होना चाहिए और इसके विपरीत)।यह सुनिश्चित करने के लिए कि वे बोर्ड तक पहुंचने में सक्षम होंगे, डेटा, बिजली और जमीन के तारों पर लंबे तारों को मिलाप करना आवश्यक होगा।

चरण 8: लकड़ी के बाहरी हिस्से का निर्माण

यह कदम वैकल्पिक है लेकिन इसकी अत्यधिक अनुशंसा की जाती है। लकड़ी का बाहरी हिस्सा न केवल वीणा को अच्छा बनाता है बल्कि सेंसर और तारों को नुकसान से भी बचाता है। लकड़ी के फ्रेम को लकड़ी से बने एक आयताकार आयताकार रिंग द्वारा बनाया जा सकता है। पाइप और सेंसर के कंकाल को फिट करने के लिए आयत के अंदर कम से कम 1-1 / 2 इंच का उद्घाटन होना चाहिए। एक बार फ्रेम के निर्माण के बाद दो छेद ड्रिल करें जो सेंसर से तारों को बाहर निकालने की अनुमति देगा और उन्हें बोर्ड से जोड़ने के लिए बाहर निकलेगा।

*नोट: यदि मरम्मत करने की आवश्यकता है या मामूली समायोजन करने की आवश्यकता है तो पाइप कंकाल को हटाने और सम्मिलित करने में सक्षम होने के लिए एक्सेस पॉइंट जोड़ने की अनुशंसा की जाती है।

चरण 9: सभी टुकड़ों को एक साथ रखना

एक बार पिछले सभी चरण समाप्त हो जाने के बाद वीणा के निर्माण का समय आ गया है। सबसे पहले पाइप के कंकाल को लकड़ी के बाहरी हिस्से के अंदर रखें। फिर सेंसर और एमिटर के लिए तारों को बोर्ड पर सही स्थान पर प्लग करें। फिर एसडीके खोलें और बोर्ड को प्रोग्राम करने के लिए डिबग बटन पर क्लिक करें। एक बार जब बोर्ड प्रोग्राम किया जाता है तो हेडफ़ोन या स्पीकर की एक जोड़ी में प्लग करें। इस पर निर्भर करता है कि कौन सा सेंसर किस पोमोड पोर्ट में समाप्त होता है, आपके वीणा के तार शायद शुरू करने के क्रम से बाहर होंगे। क्योंकि यह बताना मुश्किल हो सकता है कि इतने सारे तार शामिल होने पर कौन सा तार किस सेंसर में जाता है, हमने सॉफ्टवेयर में बिट स्थिति को बाधित करने के लिए स्ट्रिंग नंबरों को मैप करने का एक तरीका शामिल किया। "स्थैतिक int sensor_map[NUM_STRINGS]" ढूंढें और सरणी में मानों को तब तक समायोजित करें जब तक कि स्ट्रिंग्स निम्नतम से उच्चतम क्रम में न बजें।

मेनू का उपयोग सीरियल टर्मिनल (जैसे रीयलटर्म) खोलकर किया जा सकता है और बॉड दर को 115200 और डिस्प्ले को एएनएसआई पर सेट कर सकते हैं। मेनू को ऊपर और नीचे जाने के लिए w और s कुंजियों और मानों को बदलने के लिए a और d कुंजियों का उपयोग करके नेविगेट किया जा सकता है।

चरण 10: रॉक आउट

एक बार जब वीणा पूरी तरह से क्रियाशील हो जाती है। वीणा बजाओ और अपने संगीत की मधुर ध्वनि सुनो!

सिफारिश की:

MXY बोर्ड - कम बजट वाला XY प्लॉटर ड्रॉइंग रोबोट बोर्ड: 8 कदम (चित्रों के साथ)

MXY बोर्ड - लो-बजट XY प्लॉटर ड्रॉइंग रोबोट बोर्ड: मेरा लक्ष्य कम बजट को XY प्लॉटर ड्रॉइंग मशीन बनाने के लिए mXY बोर्ड को डिजाइन करना था। इसलिए मैंने एक बोर्ड तैयार किया जो उन लोगों के लिए आसान बनाता है जो इस परियोजना को बनाना चाहते हैं। पिछले प्रोजेक्ट में, 2 पीसी Nema17 स्टेपर मोटर्स का उपयोग करते हुए, यह बोर्ड आपको

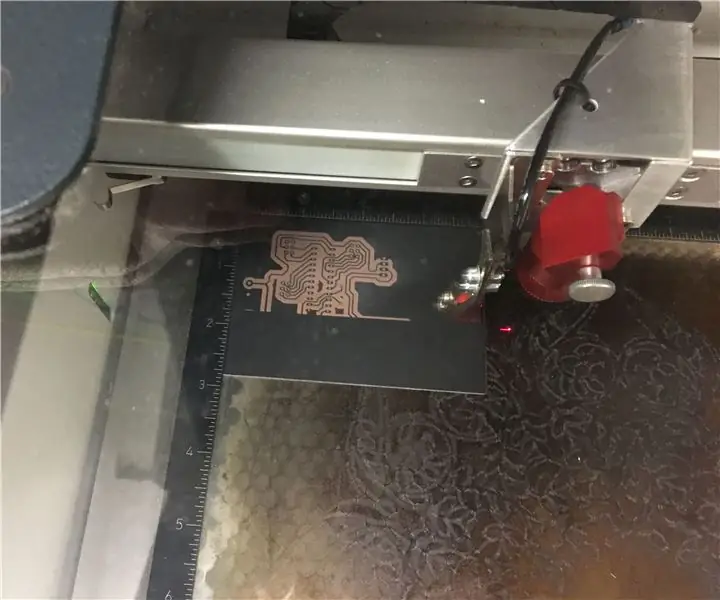

लेजर के साथ सर्किट बोर्ड बनाएं: 4 कदम (चित्रों के साथ)

लेजर के साथ सर्किट बोर्ड बनाएं: एक होममेड सर्किट बोर्ड केवल उतना ही अच्छा होता है जितना कि आप उस पर लगाते हैं। कोई फर्क नहीं पड़ता कि आप वास्तविक नक़्क़ाशी करने के लिए किस विधि का उपयोग करते हैं, आपको अभी भी अपने सर्किट की एक छवि को बोर्ड पर चिपकाने की ज़रूरत है, और सुनिश्चित करें कि यह पीछे कुरकुरा, साफ, ठोस निशान छोड़ता है

लेजर बॉक्स संगीत लेजर लाइट शो: 18 कदम (चित्रों के साथ)

लेज़र बॉक्स म्यूज़िक लेज़र लाइट शो: मैंने पहले एक इंस्ट्रक्शनल प्रकाशित किया था जिसमें बताया गया था कि म्यूज़िक लेज़र लाइट शो बनाने के लिए कंप्यूटर हार्ड ड्राइव का उपयोग कैसे किया जाता है। मैंने एक इलेक्ट्रिक बॉक्स और आरसी कार मोटर्स का उपयोग करके एक कॉम्पैक्ट संस्करण बनाने का फैसला किया। शुरू करने से पहले मुझे शायद आपको बता देना चाहिए कि लेस

मिनी सीएनसी लेजर वुड एनग्रेवर और लेजर पेपर कटर .: 18 कदम (चित्रों के साथ)

मिनी सीएनसी लेजर वुड एनग्रेवर और लेजर पेपर कटर: यह एक निर्देश है कि कैसे मैंने पुराने डीवीडी ड्राइव, 250mW लेजर का उपयोग करके एक Arduino आधारित लेजर सीएनसी वुड एनग्रेवर और थिन पेपर कटर बनाया। खेलने का क्षेत्र अधिकतम 40 मिमी x 40 मिमी है। क्या पुरानी चीजों से खुद की मशीन बनाने में मज़ा नहीं है?

Arduino बोर्ड से लेजर ड्राइवर बनाएं: 6 कदम (चित्रों के साथ)

एक Arduino बोर्ड से एक लेज़र ड्राइवर बनाएँ: यह निर्देश एक Arduino आधारित बोर्ड से 5 mW Adafruit Laser के लिए एक लेज़र ड्राइवर बनाने के लिए है। मैंने एक Arduino बोर्ड चुना क्योंकि मैं भविष्य में अपने कंप्यूटर से दूर से लेजर को नियंत्रित करना चाह सकता हूं। मैं श के लिए नमूना Arduino कोड का भी उपयोग करूंगा