विषयसूची:

- चरण 1: पीडब्लूएम मॉड्यूल का निर्माण- स्रोत फ़ाइल

- चरण 2: पीडब्लूएम मॉड्यूल का निर्माण- विवाडो सेटअप

- चरण 3: PWM मॉड्यूल का निर्माण- एक प्रोजेक्ट फ़ाइल बनाएँ

- चरण 4: पीडब्लूएम मॉड्यूल का निर्माण- ब्लॉक डिज़ाइन और बाधा फ़ाइल सेटिंग (I)

- चरण 5: पीडब्लूएम मॉड्यूल का निर्माण- ब्लॉक डिज़ाइन और बाधा फ़ाइल सेटिंग (II)

- चरण 6: पीडब्लूएम मॉड्यूल का निर्माण- ब्लॉक डिजाइन और बाधा फ़ाइल सेटिंग (III)

- चरण 7: पीडब्लूएम मॉड्यूल का निर्माण- ब्लॉक डिज़ाइन और बाधा फ़ाइल सेटिंग (IV)

- चरण 8: पीडब्लूएम मॉड्यूल का निर्माण- ब्लॉक डिजाइन और बाधा फ़ाइल सेटिंग (वी)

- चरण 9: पीडब्लूएम मॉड्यूल का निर्माण- हार्डवेयर स्थापना

- चरण 10: पीडब्लूएम मॉड्यूल का निर्माण- बिटस्ट्रीम उत्पन्न करें और एसडीके लॉन्च करें

- चरण 11: PWM मॉड्यूल का निर्माण- Xilinx SDK में एक नया एप्लिकेशन बनाएं

- चरण 12: PWM मॉड्यूल का निर्माण- प्रोजेक्ट एक्सप्लोरर (I) का अवलोकन

- चरण 13: पीडब्लूएम मॉड्यूल का निर्माण- प्रोजेक्ट एक्सप्लोरर (II) का अवलोकन

- चरण 14: पीडब्लूएम मॉड्यूल का निर्माण- प्रोजेक्ट एक्सप्लोरर (III) का अवलोकन

- चरण 15: पीडब्लूएम मॉड्यूल का निर्माण- पीडब्लूएम फंक्शन को लपेटें (I)

- चरण 16: पीडब्लूएम मॉड्यूल का निर्माण- पीडब्लूएम फंक्शन को रैप करें (II)

- चरण 17: पीडब्लूएम मॉड्यूल का निर्माण- पीडब्लूएम फंक्शन को लपेटें (III)

- चरण 18: पीडब्लूएम मॉड्यूल का निर्माण- इसे चलाएं

- चरण 19: OV7670. के साथ Digilent ZYBO पर स्ट्रीमिंग वीडियो प्रोसेसिंग

- चरण 20: पूर्ण ब्लॉक आरेख

- चरण 21: OV7670 को ZYBO. से कनेक्ट करें

- चरण 22: ब्लॉक डिजाइन बनाएं

- चरण 23: OV7670 कैमरा नियंत्रण और कैप्चर के लिए VHDL फ़ाइलें जोड़ें

- चरण 24: बाधाएँ फ़ाइल जोड़ें

- चरण 25: एचएलएस आईपी के लिए आईपी रेपो जोड़ें

- चरण 26: मॉड्यूल और आईपी जोड़ें

- चरण 27: आईपी कॉन्फ़िगरेशन सेटिंग्स

- चरण 28: पीएस आईपी ब्लॉक जोड़ें और कॉन्फ़िगर करें

- चरण 29: भाग 1. सर्वो मोटर्स के लिए पीडब्लूएम मॉड्यूल का निर्माण

- चरण 30: वीडियो इनपुट साइड कनेक्शन (एकल हाइलाइट किया गया)

- चरण 31: OV7670. से कनेक्शन

- चरण 32: वीडियो आउट साइड पर कनेक्शन

- चरण 33: ब्लॉक और कनेक्शन स्वचालन चलाएँ

- चरण ३४: एचडीएल आवरण उत्पन्न करें

- चरण 35: बिटस्ट्रीम उत्पन्न करें, एसडीके को हार्डवेयर निर्यात करें, विवाडो से एसडीके लॉन्च करें

- चरण 36: एसडीके (फ्रीआरटीओएस नहीं)

- चरण 37: फ्रीआरटीओएस कार्यान्वयन

- चरण 38: उपयोग के निर्देश

- चरण 39: संदर्भ और लिंक

वीडियो: ZYBO OV7670 कैमरा पैन/टिल्ट कंट्रोल के साथ: 39 कदम (चित्रों के साथ)

2024 लेखक: John Day | [email protected]. अंतिम बार संशोधित: 2024-01-30 09:23

केवल 2-अक्ष सर्वो PWM नियंत्रक बनाने के बारे में विस्तार से जानने के लिए चरण एक से प्रारंभ करें।

पूर्ण परियोजना के लिए बड़े पैमाने पर ब्लॉक आरेख (चरण 19) से प्रारंभ करें।

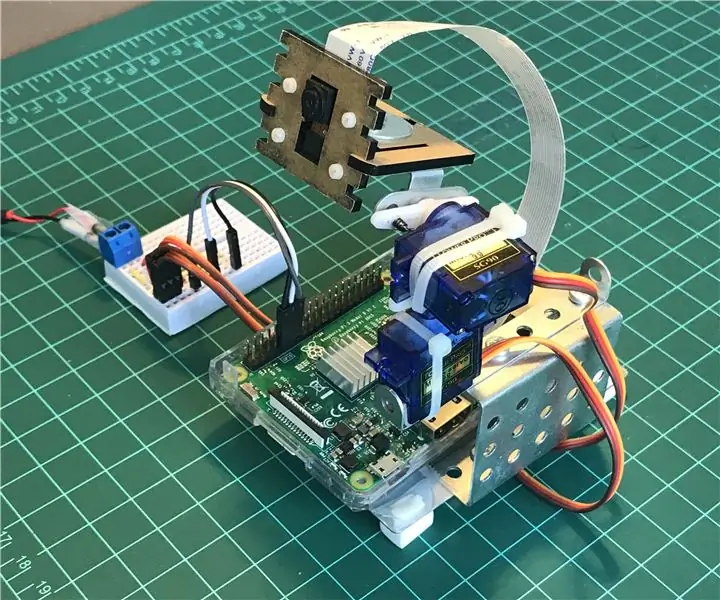

कैमरा + पैन/टिल्ट सेटअप हमने इस्तेमाल किया:

Digilent के PmodCON3 का उपयोग सर्वो को जोड़ने के लिए किया गया था।

चरण 1: पीडब्लूएम मॉड्यूल का निर्माण- स्रोत फ़ाइल

चरण 2: पीडब्लूएम मॉड्यूल का निर्माण- विवाडो सेटअप

सबसे पहले, Xilinx वेबसाइट से Vivado Design Suite डाउनलोड करें। विवाडो सॉफ्टवेयर डेवलपमेंट किट (एसडीके) सहित सभी डिज़ाइन सूट स्थापित करें। यह प्रोजेक्ट 2017.2 संस्करण का उपयोग करता है।

इस बीच, Digilent Adept 2 को Zybo बोर्ड ड्राइवर के रूप में भी स्थापित किया जाना चाहिए।

चरण 3: PWM मॉड्यूल का निर्माण- एक प्रोजेक्ट फ़ाइल बनाएँ

प्रोजेक्ट फ़ाइल बनाने से पहले, आपको यह सुनिश्चित करना चाहिए कि आपने Zybo फ़ाइल को यहाँ ट्यूटोरियल के रूप में ठीक से स्थापित कर लिया है:

विवाडो संस्करण 2015.1 और बाद में बोर्ड फ़ाइल स्थापना

विवाडो 2017.2 खोलें। क्विक स्टार्ट पर, क्रिएट प्रोजेक्ट -> नेक्स्ट -> प्रोजेक्ट नेम (अपने प्रोजेक्ट का नाम यहां नाम दें) -> प्रोजेक्ट टाइप पर क्लिक करें। प्रोजेक्ट प्रकार पर, RTL प्रोजेक्ट चुनें और "इस समय स्रोत निर्दिष्ट न करें" पर निशान लगाएं। अगला, डिफ़ॉल्ट भाग के लिए, प्रदर्शन नाम के रूप में "बोर्ड" और "ज़ीबो" चुनें। अगला, प्रोजेक्ट शुरू करने के लिए समाप्त पर क्लिक करें।

चरण 4: पीडब्लूएम मॉड्यूल का निर्माण- ब्लॉक डिज़ाइन और बाधा फ़ाइल सेटिंग (I)

फ्लो नेविगेटर पर, ""ब्लॉक डिज़ाइन बनाएं" पर क्लिक करें, फिर ओके दबाएं। आवश्यक IP जोड़ने के लिए "+" चिह्न पर क्लिक करें। जोड़ें:

- एक ZYNQ7 प्रोसेसिंग सिस्टम दो AXI टाइमर

- दो AXI टाइमर

चरण 5: पीडब्लूएम मॉड्यूल का निर्माण- ब्लॉक डिज़ाइन और बाधा फ़ाइल सेटिंग (II)

IP जोड़ने के बाद, ब्लॉक ऑटोमेशन और कनेक्शन ऑटोमेशन चलाएँ। एक बार ऑटोमेशन पूरा हो जाने के बाद, "axi_timer_0" ब्लॉक पर, pwm0 -> MakeExternal पर राइट क्लिक करें। pwm0 बाहरी पिन को pwm_Xaxis नाम दें। इसके अलावा, उपरोक्त प्रक्रिया को "axi_timer_1" ब्लॉक पर दोहराएं और pwm0 बाहरी पिन को pwm_Zaxis नाम दें।

चरण 6: पीडब्लूएम मॉड्यूल का निर्माण- ब्लॉक डिजाइन और बाधा फ़ाइल सेटिंग (III)

ध्यान दें कि हर बार जब हम विवाडो में ब्लॉक डिज़ाइन को पूरा करते हैं, तो हमें एक एचडीएल रैपर बनाने की आवश्यकता होती है। चूंकि यह प्रत्येक प्रोजेक्ट के लिए शीर्ष-स्तरीय मॉड्यूल होगा।

चरण 7: पीडब्लूएम मॉड्यूल का निर्माण- ब्लॉक डिज़ाइन और बाधा फ़ाइल सेटिंग (IV)

अब, हमें अपने ब्लॉक आरेख से जुड़े पिनों को असाइन करने के लिए अपनी बाधा फ़ाइल सेट करने की आवश्यकता है। ब्लॉक डिज़ाइन विंडो को बंद करें, स्रोत टैब पर, "स्रोत जोड़ें"-> बाधाएँ जोड़ें या बनाएँ-> Zybo-Master.xdc को हमारी बाधा फ़ाइलों के रूप में जोड़ें।

चरण 8: पीडब्लूएम मॉड्यूल का निर्माण- ब्लॉक डिजाइन और बाधा फ़ाइल सेटिंग (वी)

बाधा फ़ाइल Zybo-Master.xdc को बाधा फ़ोल्डर से खोलें, उन पोर्ट को अनकम्मेंट करें जिन्हें हम आउटपुट सिग्नल के रूप में निर्दिष्ट करना चाहते हैं और "get_ports{XXXX}" का नाम बदलें, जो XXXX ब्लॉक आरेख में नामित बाहरी पिन को दर्शाता है। बाधा फ़ाइल की सेटिंग को चित्र में दिखाया गया है।

चरण 9: पीडब्लूएम मॉड्यूल का निर्माण- हार्डवेयर स्थापना

सर्वो मोटर्स को Pmod CON3 से कनेक्ट करें। TowerPro SG90 सर्वो मोटर मॉडल है जिसे हमने इस परियोजना में उपयोग किया है। सर्वो मोटर तारों के लिए, नारंगी तार Pmod CON3 में SIG पिन से जुड़े PWM सिग्नल का प्रतिनिधित्व करता है। लाल तार Vcc, Pmod CON3 में VS पिन से जुड़ा एक पावर वायर है। अंत में, ब्राउन वायर Gnd GND पिन से जुड़ा एक ग्राउंड वायर है। इसके बाद, Zybo बोर्ड में JD पोर्ट की ऊपरी पंक्ति में Pmod CON3 डालें।

चरण 10: पीडब्लूएम मॉड्यूल का निर्माण- बिटस्ट्रीम उत्पन्न करें और एसडीके लॉन्च करें

1. प्रोजेक्ट नेविगेटर टैब में, जनरेट बिटस्ट्रीम चलाएँ।

2.निर्यात हार्डवेयर: फ़ाइल> निर्यात> निर्यात हार्डवेयर-> "बिटस्ट्रीम शामिल करें" पर चिह्नित करें -> ठीक है 3. एसडीके लॉन्च करें: फ़ाइल -> एसडीके लॉन्च करें।

चरण 11: PWM मॉड्यूल का निर्माण- Xilinx SDK में एक नया एप्लिकेशन बनाएं

एक नयी एप्लीकेशन बनाऊ:

फ़ाइल> नया> एप्लिकेशन प्रोजेक्ट -> अपनी परियोजना का नाम दर्ज करें -> समाप्त करें

प्रोजेक्ट एक्सप्लोरर के तहत तीन फोल्डर होने चाहिए।

इस मामले में, "डिज़ाइन_1_wrapper_hw_platform_0" विवाडो द्वारा पहले निर्यात किया गया फ़ोल्डर है। Axis_2_PWM_SDK_bsp बोर्ड सपोर्ट पैकेज फोल्डर है। और Axis_2_PWM_SDK SDK में हमारा मुख्य प्रोजेक्ट फ़ोल्डर है। आप Axis_2_PWM_SDK के "src" फ़ोल्डर के अंतर्गत "helloworld.c" फ़ाइल देख सकते हैं, जहाँ "helloworld.c" मुख्य फ़ाइल है।

चरण 12: PWM मॉड्यूल का निर्माण- प्रोजेक्ट एक्सप्लोरर (I) का अवलोकन

आइए प्रोजेक्ट एक्सप्लोरर के तहत कुछ फाइलों की जांच करें। सबसे पहले, "डिज़ाइन_1_wrapper_hw_platform_0" फ़ोल्डर में, "system.hdf" खोलें। यह फ़ाइल हमारे डिज़ाइन में मौजूद प्रोसेसर ps7_cortex9 और IP ब्लॉक के लिए एड्रेस मैप को प्रदर्शित करती है।

चरण 13: पीडब्लूएम मॉड्यूल का निर्माण- प्रोजेक्ट एक्सप्लोरर (II) का अवलोकन

फिर, "एक्सिस_2_PWM_SDK_bsp" फ़ोल्डर के अंतर्गत "शामिल करें" और "libsrc" फ़ाइल की जाँच करें। यहां लाइब्रेरी फाइलें हमें "प्लेइंग" रजिस्टरों के बिना हार्डवेयर बाह्य उपकरणों के साथ बातचीत करने में सक्षम बनाती हैं।

चरण 14: पीडब्लूएम मॉड्यूल का निर्माण- प्रोजेक्ट एक्सप्लोरर (III) का अवलोकन

बसपा प्रलेखन के माध्यम से, xtmrctr.h को AXI टाइमर से संबंधित एक Xilinx टाइमर नियंत्रण पुस्तकालय के रूप में पाया जाता है। आमतौर पर, हम यहां वांछित PWM फ़ंक्शन पा सकते हैं। हालाँकि, यदि आप दस्तावेज़ "tmrctr_v4_3" पढ़ते हैं, तो यह दर्शाता है कि ड्राइवर वर्तमान में डिवाइस के PWM संचालन का समर्थन नहीं करता है। PWM फ़ंक्शन में कमी के कारण, हमें अपने PWM फ़ंक्शन को xtmrctr.h और AXI टाइमर v2.0 LogiCORE IP उत्पाद गाइड की सहायता से लपेटना होगा।

चरण 15: पीडब्लूएम मॉड्यूल का निर्माण- पीडब्लूएम फंक्शन को लपेटें (I)

मुख्य फ़ाइल "helloworld.c" पर वापस, निम्न शीर्षलेख फ़ाइलें शामिल करें:

चरण 16: पीडब्लूएम मॉड्यूल का निर्माण- पीडब्लूएम फंक्शन को रैप करें (II)

"xparameters.h" के माध्यम से दो AXI TImer के आधार पते को परिभाषित करें।

चरण 17: पीडब्लूएम मॉड्यूल का निर्माण- पीडब्लूएम फंक्शन को लपेटें (III)

वांछित PWM फ़ंक्शन बनाएँ।

ड्यूटी_वल: डिग्री मान को कर्तव्य चक्र में परिवर्तित करता है। PWM_Freq_Duty: PWM उत्पन्न करने के लिए वांछित आवृत्ति और कर्तव्य चक्र सेट करें। घड़ी की अवधि भी नियत की जानी चाहिए।

PWM_START: PWM रजिस्टर एड्रेस असाइन करें और PWM जेनरेट करना शुरू करें।

PWM_STOP: PWM रजिस्टर एड्रेस असाइन करें और PWM जेनरेट करना बंद करें।

बाकी डेमो कोड "Helloworld.c" में "Axis_2_PWM_SDK" के तहत दिखाया गया है।

चरण 18: पीडब्लूएम मॉड्यूल का निर्माण- इसे चलाएं

1. एसडीके के माध्यम से एफपीजीए प्रोग्राम करें

- यूएसबी पोर्ट के माध्यम से ज़ीबो बोर्ड को पीसी से कनेक्ट करें।

- Xilinx टूल्स -> प्रोग्राम FPGA

2. कार्यक्रम चलाएं

"रन" आइकन पर क्लिक करें और मेनू ड्रॉप डाउन -> रन अस -> हार्डवेयर पर लॉन्च करें

3.एसडीके टर्मिनल

- एसडीके टर्मिनल खोलें -> सीरियल पोर्ट से कनेक्ट करें -> ठीक

- प्रोग्राम चलाएँ। यदि डेमो कोड सफलतापूर्वक चलता है, तो आपको "इनिशियलाइज़ेशन हो गया!" देखना चाहिए। एसडीके टर्मिनल पर।

चरण 19: OV7670. के साथ Digilent ZYBO पर स्ट्रीमिंग वीडियो प्रोसेसिंग

पूरी आर्काइव फाइल संलग्न है।

चरण 20: पूर्ण ब्लॉक आरेख

यह परियोजना में सभी कनेक्शनों और आईपी ब्लॉकों का पूरा आरेख दिखाता है

चरण 21: OV7670 को ZYBO. से कनेक्ट करें

ov7670 मॉड्यूल को ZYBO Pmods से वायर करने के लिए एक कनेक्शन बनाएं

डेटा Pmod Pmod D. है

नियंत्रण Pmod Pmod C. है

इसके अतिरिक्त, इस ट्यूटोरियल के पहले भाग में बताए अनुसार PmodCON3 और सर्वो को कनेक्ट करें

चरण 22: ब्लॉक डिजाइन बनाएं

फ़्लो नेविगेटर में, "ब्लॉक डिज़ाइन बनाएँ" पर क्लिक करें, फिर ओके दबाएँ।

चरण 23: OV7670 कैमरा नियंत्रण और कैप्चर के लिए VHDL फ़ाइलें जोड़ें

इस चरण से जुड़ी VHDL फ़ाइलों को प्रोजेक्ट में जोड़ें

चरण 24: बाधाएँ फ़ाइल जोड़ें

अपनी परियोजना में संलग्न बाधा फ़ाइल जोड़ें।

चरण 25: एचएलएस आईपी के लिए आईपी रेपो जोड़ें

ज़िप फ़ाइल को संलग्न करें और इसे "HLS_repo" नामक एक नई निर्देशिका (फ़ोल्डर) में इसी तरह नामित एक नए फ़ोल्डर में अनज़िप करें।

IP कैटलॉग में जाकर अपने प्रोजेक्ट में एक IP रिपॉजिटरी जोड़ें और "Repository जोड़ें …" का चयन करके राइट-क्लिक करें।

अपनी "HLS_repo" निर्देशिका पर नेविगेट करें और इसे चुनें।

वैकल्पिक: अपने लिए एचएलएस वीडियो प्रोसेसिंग ब्लॉक बनाएं!

चरण 26: मॉड्यूल और आईपी जोड़ें

पृष्ठभूमि पर राइट क्लिक करके और "मॉड्यूल जोड़ें …" का चयन करके ov7670_axi_stream_capture, debounce और ov7670_controller मॉड्यूल को ब्लॉक आरेख में जोड़ें।

इसी तरह, आईपी जोड़ें:

- एचएलएस_वीडियो_ट्रैक

- वीडियो फ्रेम बफर लिखें

- वीडियो फ्रेम बफर पढ़ें

- वीडियो समय नियंत्रक

- AXI4-स्ट्रीम से वीडियो आउट

- "स्लाइस" के 3

- लगातार

- 2 AXI टाइमर

चरण 27: आईपी कॉन्फ़िगरेशन सेटिंग्स

जैसा कि तस्वीरों में दिखाया गया है

चरण 28: पीएस आईपी ब्लॉक जोड़ें और कॉन्फ़िगर करें

ZYNQ7 प्रोसेसिंग सिस्टम को ब्लॉक डायग्राम में जोड़ें

कॉन्फ़िगरेशन संपादित करें:

-

पीएस-पीएल विन्यास

-

हिमाचल प्रदेश

- एस एचपी सक्षम करें 0

- एस एचपी सक्षम करें 1

-

-

घड़ी विन्यास

-

पीएल फैब्रिक घड़ियां

- FCLK_0 100MHz पर

- FCLK_1 25 मेगाहर्ट्ज पर (आउटपुटक्लॉक)

- FLCK_2 35MHz पर (<=50MHz) (कैमरा घड़ी)

-

चरण 29: भाग 1. सर्वो मोटर्स के लिए पीडब्लूएम मॉड्यूल का निर्माण

axi_timer_0 pwm0 को नए आउटपुट पोर्ट pwm_Xaxis में लाएं

axi_timer_1 pwm0 को नए आउटपुट पोर्ट pwm_Zaxis में लाएं

चरण 30: वीडियो इनपुट साइड कनेक्शन (एकल हाइलाइट किया गया)

वीडियो इनपुट साइड आईपी ब्लॉक को सही तरीके से कनेक्ट करें

(* इन कनेक्शनों को कनेक्शन स्वचालन के दौरान सही विकल्प चुनकर बनाया जाना चाहिए) axi_stream_capture से "aclk" जाता है:

- वीडियो फ्रेम बफर पर ap_clk लिखें

- एचएलएस वीडियो स्ट्रीम प्रोसेसिंग ब्लॉक पर ap_clk

- *वीडियो फ्रेम बफर से AXI स्मार्टकनेक्ट IP पर aclk S_AXI_HP0 को लिखें

- * एचएलएस वीडियो प्रोसेसिंग ब्लॉक के S_AXI चैनलों के लिए AXI इंटरकनेक्ट IP के चैनलों के अनुरूप aclk और PS ब्लॉक पर वीडियो फ्रेम बफर S_AXI_HP0_ACLK लिखें

वीडियो स्ट्रीम सिग्नल केवल श्रृंखला में कैप्चर ब्लॉक से Zynq मेमोरी इंटरफ़ेस से जुड़ा हुआ है।

- वीडियो कैप्चर ब्लॉक से एचएलएस प्रोसेसिंग ब्लॉक तक जाता है।

- एचएलएस ब्लॉक से संसाधित वीडियो फ्रेम बफर राइट ब्लॉक में जाता है।

- * फ्रेम बफर राइट ब्लॉक Zynq PS ब्लॉक पर HP0 इंटरफ़ेस से जुड़ता है।

- कैप्चर ब्लॉक के आउटपुट से m_axis_tuser सिग्नल को मैन्युअल रूप से HLS प्रोसेसिंग ब्लॉक पर video_in_TUSER इनपुट सिग्नल और एक ही ब्लॉक पर ap_start सिग्नल दोनों के लिए वायर्ड किया जाता है।

TUSER (ट्यूसर) सिग्नल का उपयोग AXI वीडियो स्ट्रीम प्रोटोकॉल द्वारा वीडियो के एक फ्रेम की शुरुआत को इंगित करने के लिए किया जाता है। AP_Start HLS ब्लॉक को प्रोसेसिंग शुरू करने के लिए कहता है। इस प्रकार हम प्रत्येक फ्रेम को संसाधित करने के लिए HLS ब्लॉक को ट्रिगर करने के लिए ट्यूसर का उपयोग कर रहे हैं। में आता है। बस के एक सिग्नल को जोड़ने और इसे इस तरह से विभाजित करते समय इसे बाकी बस के सामान्य समाप्ति बिंदु से जोड़ना भी आवश्यक है। विवाडो मानता है कि यदि आप सिग्नल को मैन्युअल रूप से कनेक्ट कर रहे हैं जिसे आप डिस्कनेक्ट करना चाहते हैं तो यह सामान्य रूप से कनेक्ट होगा।

IP ब्लॉकों की कॉन्फ़िगरेशन सेटिंग्स:

वीडियो फ्रेम बफर लिखें:

वीडियो प्रारूप: RGB8

प्रति घड़ी 1 नमूना अधिकतम कॉलम: 1280 (>=640) अधिकतम पंक्तियाँ: 960 (>=480) अधिकतम डेटा चौड़ाई: 8

चरण 31: OV7670. से कनेक्शन

Ov7670_axi_stream_capture ब्लॉक पर

- सभी इनपुट बाहरी बनाएं (पिन पर राइट क्लिक करें और मेनू से चुनें, या बायां क्लिक-> ctrl + T)

- नामों को वैसे ही छोड़ दें जैसे वे हैं

Ov7670_controller ब्लॉक पर

- सभी ब्लॉक आउटपुट को बाहरी बनाएं

- कॉन्फिग_फिनिश्ड पोर्ट का नाम बदलकर लेड0 कर दें

- clk को कैमराक्लॉक से कनेक्ट करें (<=50MHz) (FCLK_2)

डेब्यू ब्लॉक पर

- बटन 1 इनपुट को बाहरी इनपुट पोर्ट से कनेक्ट करें जिसे btn0. कहा जाता है

- ov7670_controller IP ब्लॉक पर आउट1 को फिर से भेजें लाइन से कनेक्ट करें

- बटन 2 इनपुट को बाहरी इनपुट पोर्ट से कनेक्ट करें जिसे btn3. कहा जाता है

- वीडियो कैप्चर क्लॉक डोमेन के लिए प्रोसेसर सिस्टम रीसेट IP पर out2n को ext_reset_in इनपुट से कनेक्ट करें। (* आईपी उत्पन्न होने के बाद ऐसा करने की आवश्यकता हो सकती है*)

- clk को कैमराक्लॉक से कनेक्ट करें (<=50MHz) (FCLK_2)

चरण 32: वीडियो आउट साइड पर कनेक्शन

ब्लॉक वीडियो टाइमिंग कंट्रोलर (VTC), AXI4-स्ट्रीम से वीडियो आउट, और स्लाइस के लिए कनेक्शन

- Vid_io_out_clk और VTC clk. के लिए 25MHz घड़ी (FCLK_1) का उपयोग करें

- AXI4-स्ट्रीम से वीडियो आउट पर aclk के लिए 100MHz घड़ी (FCLK_0) का उपयोग करें

- vtimeing_out से vtimeing_in

- वीडियो फ्रेम बफर पढ़ें m_axis_video AXI4-स्ट्रीम से वीडियो आउट वीडियो_इन पर जाता है

- vtg_ce gen_clken को जाता है

- VTC clken, aclken, vid_io_out_ce को कॉन्स्टेंट डाउट से बाँधें[0:0]

- vid_hsync और vid_vsync को क्रमशः बाहरी आउटपुट पोर्ट vga_hs और vga_vs पर लाएं। (चित्रित नहीं)

स्लाइस:

-

संलग्न चित्रों में दिखाए अनुसार स्लाइस को सेटअप किया जाना चाहिए

- ब्लॉक का नाम बदलकर स्लाइस_रेड, स्लाइस_ग्रीन और स्लाइस_ब्लू कर दें

- ब्लॉक के नाम के अनुसार छवियों में दिखाए गए अनुसार सेटअप स्लाइस रेंज

- छवि में दिखाए गए अनुसार प्रत्येक स्लाइस आउटपुट को बाहरी पोर्ट आउटपुट से कनेक्ट करें।

- vid_data[२३:०] प्रत्येक स्लाइस के लिए इनपुट से जुड़ता है (दिन [२३:०])

चरण 33: ब्लॉक और कनेक्शन स्वचालन चलाएँ

ZYNQ7 PS ब्लॉक से चीजों को जोड़ने के लिए ब्लॉक ऑटोमेशन चलाएँ। जैसा कि चित्र द्वारा दिखाया गया है।

सभी इंटरकनेक्शन आईपी बनाने के लिए कनेक्शन ऑटोमेशन चलाएं। प्रत्येक चित्र में सभी विकल्पों पर पूरा ध्यान दें।

डिबॉन्स ब्लॉक पर, out2n को वीडियो कैप्चर क्लॉक डोमेन प्रोसेसर सिस्टम रीसेट ext_reset_in इनपुट से कनेक्ट करें।

चरण ३४: एचडीएल आवरण उत्पन्न करें

अपने ब्लॉक डिजाइन के लिए एचडीएल रैपर जेनरेट करें।

इसे शीर्ष मॉड्यूल के रूप में सेट करें।

चरण 35: बिटस्ट्रीम उत्पन्न करें, एसडीके को हार्डवेयर निर्यात करें, विवाडो से एसडीके लॉन्च करें

निर्यात में बिटस्ट्रीम को शामिल करना सुनिश्चित करें।

बिटस्ट्रीम के निर्माण में बहुत लंबा समय लग सकता है।

फिर एसडीके लॉन्च करें

चरण 36: एसडीके (फ्रीआरटीओएस नहीं)

यह संस्करण कोड को अच्छी तरह से संघनित करते हुए, FreeRTOS का उपयोग किए बिना सब कुछ करता है।

हार्डवेयर डिज़ाइन के आधार पर एक स्टैंडअलोन बीएसपी बनाएं। डिफ़ॉल्ट विकल्प ठीक होना चाहिए। सुनिश्चित करें कि बसपा स्रोत उत्पन्न हो गए हैं।

चित्र में दिखाए अनुसार ऐप बनाएं। (खाली आवेदन)

ऑटोजेनरेटेड मुख्य हटाएं और संलग्न फाइलों को आयात करें।

चरण 37: फ्रीआरटीओएस कार्यान्वयन

यह संस्करण FreeRTOS का उपयोग करता है। हार्डवेयर डिज़ाइन के आधार पर एक FreeRTOS901 BSP बनाएँ। डिफ़ॉल्ट विकल्प ठीक होना चाहिए। सुनिश्चित करें कि बसपा स्रोत उत्पन्न हो गए हैं।

चित्र में दिखाए अनुसार ऐप बनाएं। (खाली आवेदन)

ऑटोजेनरेटेड मुख्य हटाएं और संलग्न फाइलों को आयात करें।

चरण 38: उपयोग के निर्देश

इस प्रोजेक्ट को चलाना थोड़ा मुश्किल है। क्रम में चरणों का पालन करें।

सुनिश्चित करें कि आपका ZYBO चालू होने पर कुछ भी स्वयं लोड नहीं कर रहा है। इसका मतलब है कि हो गया एलईडी प्रकाश नहीं करना चाहिए। ऐसा करने का एक तरीका बूट स्रोत जम्पर को JTAG पर सेट करना है।

वह प्रोजेक्ट खोलें (फ्रीआरटीओएस या नहीं) जिसे आप एसडीके से प्रोग्राम करना चाहते हैं

- अपना ZYBO चालू करें। हो गया एलईडी प्रकाश नहीं करना चाहिए।

- FPGA को बिट फ़ाइल के साथ प्रोग्राम करें। हो गया एलईडी प्रकाश करना चाहिए। LED0 को प्रकाश नहीं करना चाहिए।

- कोड चलाएँ (यदि आप ऐसा कर रहे हैं तो स्टार्ट ब्रेकपॉइंट से आगे जाना याद रखें)।

इस बिंदु पर आपको अपने वीजीए डिस्प्ले पर एक आउटपुट मिलना चाहिए।

पुनः आरंभ करने के लिए (यदि यह बग या जो भी हो): जल्दी से PS-SRST बटन पर टैप करें या ZYBO को बंद करें और फिर वापस चालू करें। चरण 2 से जारी रखें।

डिबगर के साथ प्रोसेसर को रोकने से कैमरा हिलने के बजाय स्थिति को बनाए रखेगा। वीडियो स्ट्रीम वैसे भी जारी रहेगी।

चरण 39: संदर्भ और लिंक

Xilinx संदर्भ मार्गदर्शिकाएँ और दस्तावेज़ीकरण:

- PG044 - AXI-स्ट्रीम से वीडियो आउट

- PG278 - वीडियो फ़्रेम बफ़र पढ़ें/लिखें

अन्य लिंक:

- लॉरी का ब्लॉग - वीडीएमए इनपुट

- लॉरी का ब्लॉग - OV7670 से VGA आउटपुट BRAM का उपयोग करके

- हैम्स्टरवर्क्स विकी, माइक फील्ड्स द्वारा, OV7670 कोड का मूल स्रोत

- बुनियादी समय विनिर्देशों को दर्शाने वाली डेटाशीट

सिफारिश की:

डीएसएलआर टाइम लैप्स के लिए पैन और टिल्ट मैकेनिज्म: 7 स्टेप्स (चित्रों के साथ)

डीएसएलआर टाइम लैप्स के लिए पैन और टिल्ट मैकेनिज्म: मेरे पास कुछ स्टेपर मोटर्स पड़ी थीं और वास्तव में कुछ अच्छा बनाने के लिए उनका उपयोग करना चाहता था। मैंने तय किया कि मैं अपने डीएसएलआर कैमरे के लिए एक पैन और टिल्ट सिस्टम बनाऊंगा ताकि मैं कूल टाइम लैप्स बना सकूं। आपको जिन वस्तुओं की आवश्यकता होगी: 2x स्टेपर मोटर्स -htt

IOT123 - सोलर ट्रैकर - टिल्ट/पैन, पैनल फ्रेम, LDR माउंट्स रिग: 9 स्टेप्स (चित्रों के साथ)

IOT123 - सोलर ट्रैकर - टिल्ट/पैन, पैनल फ्रेम, LDR माउंट्स रिग: डुअल एक्सिस सोलर ट्रैकर्स के लिए अधिकांश DIY डिजाइन "बाहर" 9G माइक्रो सर्वो पर आधारित हैं जो वास्तव में सौर सेल, माइक्रो-कंट्रोलर, बैटरी और आवास के एक जोड़े के चारों ओर धकेलने के लिए अंडर-रेटेड हैं। आप चारों ओर डिजाइन कर सकते हैं

पैन-टिल्ट मल्टी सर्वो नियंत्रण: 11 चरण (चित्रों के साथ)

पैन-टिल्ट मल्टी सर्वो कंट्रोल: इस ट्यूटोरियल में, हम यह पता लगाएंगे कि रास्पबेरी पाई पर पायथन का उपयोग करके कई सर्वो को कैसे नियंत्रित किया जाए। हमारा लक्ष्य एक कैमरा (एक PiCam) की स्थिति के लिए एक PAN/TILT तंत्र होगा। यहां आप देख सकते हैं कि हमारा अंतिम प्रोजेक्ट कैसे काम करेगा: कंट्रोल सर्वो कंट्रोल लूप टेस्ट:

रिमोट नियंत्रित पैन और टिल्ट हेड: 7 कदम

रिमोट कंट्रोल्ड पैन और टिल्ट हेड: मैं हमेशा रिमोट से नियंत्रित पैन और टिल्ट हेड चाहता था। शायद यह मेरे वीडियो कैमरा, रबर बैंड शूटर या वाटर गन लक्ष्य के लिए था। यह वास्तव में कोई फर्क नहीं पड़ता कि आप शीर्ष डेक पर क्या डालते हैं (जब तक कि यह बहुत भारी न हो), इस छोटे से प्रोजेक्ट के साथ

कैमरा डी वीडियो एन कैरो डी रेडियो कंट्रोल / आर / सी ट्रक पर वीडियो कैमरा: 5 कदम

कैमरा डी वीडियो एन कैरो डी रेडियो कंट्रोल / आर / सी ट्रक पर वीडियो कैमरा: एस्टे इंस्ट्रक्शनेबल प्रेजेंटैडो एन एस्पानोल ई इंगल्स। ये निर्देश स्पेनिश और अंग्रेजी में प्रस्तुत किए गए हैं